Part Number: DP83TC812EVM-MC

Other Parts Discussed in Thread: DP83TC812R-Q1

Hi,

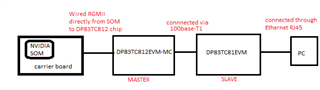

We are developing a board with a 100Base-T1 interface using the DP83TC812R-Q1 chip.

We were checking this with our carrier board, like the below connection.

We have isolated the DP83867ERGZR chip connections.

Link was detected. communication is proper through MDIO,MDC line.

but we can't able to ping.

it shows * Network unreachable*

I have attached the log for this issue below.

DRIVER LOADED

nvidia@tegra-ubuntu:~$ sudo dmesg | grep -i eth

[sudo] password for nvidia:

[ 0.000000] psci: probing for conduit method from DT.

[ 4.223949] hns3: Hisilicon Ethernet Network Driver for Hip08 Family - version

[ 4.248077] igb: Intel(R) Gigabit Ethernet Network Driver

[ 4.296360] usbcore: registered new interface driver cdc_ether

[ 7.424211] optee: probing for conduit method.

[ 12.965592] nvethernet 2310000.ethernet: Adding to iommu group 51

[ 12.971985] nvethernet 2310000.ethernet: failed to read skip mac reset flag, default 0

[ 12.980167] nvethernet 2310000.ethernet: failed to read MDIO address

[ 12.986718] nvethernet 2310000.ethernet: Failed to read nvida,pause_frames, so setting to default support as disable

[ 12.997548] nvethernet 2310000.ethernet: setting to default DMA bit mask

[ 13.004464] nvethernet 2310000.ethernet: missing nvidia,pad_auto_cal_pu_offset, setting default 0

[ 13.013583] nvethernet 2310000.ethernet: missing nvidia,pad_auto_cal_pd_offset, setting default 0

[ 13.039802] nvethernet 2310000.ethernet: Ethernet MAC address: 48:b0:2d:94:41:3d

[ 13.047748] nvethernet 2310000.ethernet: macsec param in DT is missing or disabled

[ 13.055538] nvethernet 2310000.ethernet: Macsec not supported/Not enabled in DT

[ 13.065800] nvethernet 2310000.ethernet: eth0 (HW ver: 53) created with 8 DMA channels

[ 18.883875] TI DP83TC812CS2.0 2310000.ethernet:00: ~~~~~~~~~~~LOADED~~~~~~~~~~~

[ 18.884279] mdio_bus 2310000.ethernet: ~~~~~~~~~~printing phy phy at address 0

[ 19.100012] TI DP83TC812CS2.0 2310000.ethernet:00: ~~~~~~~~~~~LOADED~~~~~~~~~~~

[ 63.126826] IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

[ 63.127398] nvethernet 2310000.ethernet eth0: Link is Up - 100Mbps/Full - flow control off

DRIVER STRAP REGISTER

nvidia@tegra-ubuntu:~$ sudo dmesg | grep -i dp83

[ 18.670154] dp83812_read_straps: Strap is 0x4280

[ 18.883875] TI DP83TC812CS2.0 2310000.ethernet:00: ~~~~~~~~~~~LOADED~~~~~~~~~~~

[ 18.884494] dp83812_read_straps: Strap is 0x4280

[ 19.100012] TI DP83TC812CS2.0 2310000.ethernet:00: ~~~~~~~~~~~LOADED~~~~~~~~~~~

NO IP assigned

nvidia@tegra-ubuntu:~$ ifconfig

eth0: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500

inet6 fe80::ae9f:68c9:9e64:82d prefixlen 64 scopeid 0x20<link>

ether 48:b0:2d:94:41:3d txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 73 bytes 12523 (12.5 KB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 1110 bytes 71114 (71.1 KB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 1110 bytes 71114 (71.1 KB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

ERROR MESSAGE

nvidia@tegra-ubuntu:~$ [ 264.950727] nvethernet 2310000.ethernet: Failed to report error: reporter ID: 0x0, Error code: 0x1001, return: -19

PING tried with both static and dynamic ip configuration.

nvidia@tegra-ubuntu:~$ ping 8.8.8.8

ping: connect: Network is unreachable

nvidia@tegra-ubuntu:~$ sudo ethtool eth0

[sudo] password for nvidia:

Settings for eth0:

Supported ports: [ TP MII ]

Supported link modes: Not reported

Supported pause frame use: Symmetric Receive-only

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: Not reported

Advertised pause frame use: No

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 100Mb/s

Duplex: Full

Port: Twisted Pair

PHYAD: 0

Transceiver: internal

Auto-negotiation: off

MDI-X: Unknown

Supports Wake-on: d

Wake-on: d

Current message level: 0x00000000 (0)

Link detected: yes