Hi expert,

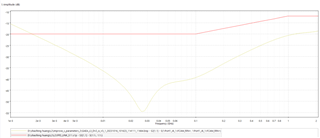

I'm using Des-954 paired with Ser-943.(4Gbs mode) Even if I use the PoC components recommended by TI D/S, it cannot pass the simulation. Simulation result shows that S11&S21 will fail at 1MHz~2MHz.

The 10uH inductor is too small to block 1MHz signal. In comparison, the recommended 100uh inductor in 2Gbs mode looks more reasonable, but why do their simulations requirement to be the same? They all start from 1MHz and the limits are the same.(channel spec: FPD3_91X_93X_95X_96X-Channel-Requirements-ADAS chipsets-0.8.1)

I checked the layout and it looks good, smooth and within 2 inch. And the failure position is at low frequency. I think this depends on the large inductor.

So, could you help pass this simulation and answer some questions:

- The recommended PoC components also fails the simulation. Does TI have a simulation report?

- Why does the simulation require starting from 1MHZ? It seems very strict.

- The requirements for 2G and 4G modes are the same (except for the cutoff frequency), but the recommended PoC structures are different?

Best regards,

Harvey Nie