Part Number: TCA9548A

Hi

My customer faced a master interface signal issue, which can be described as following:

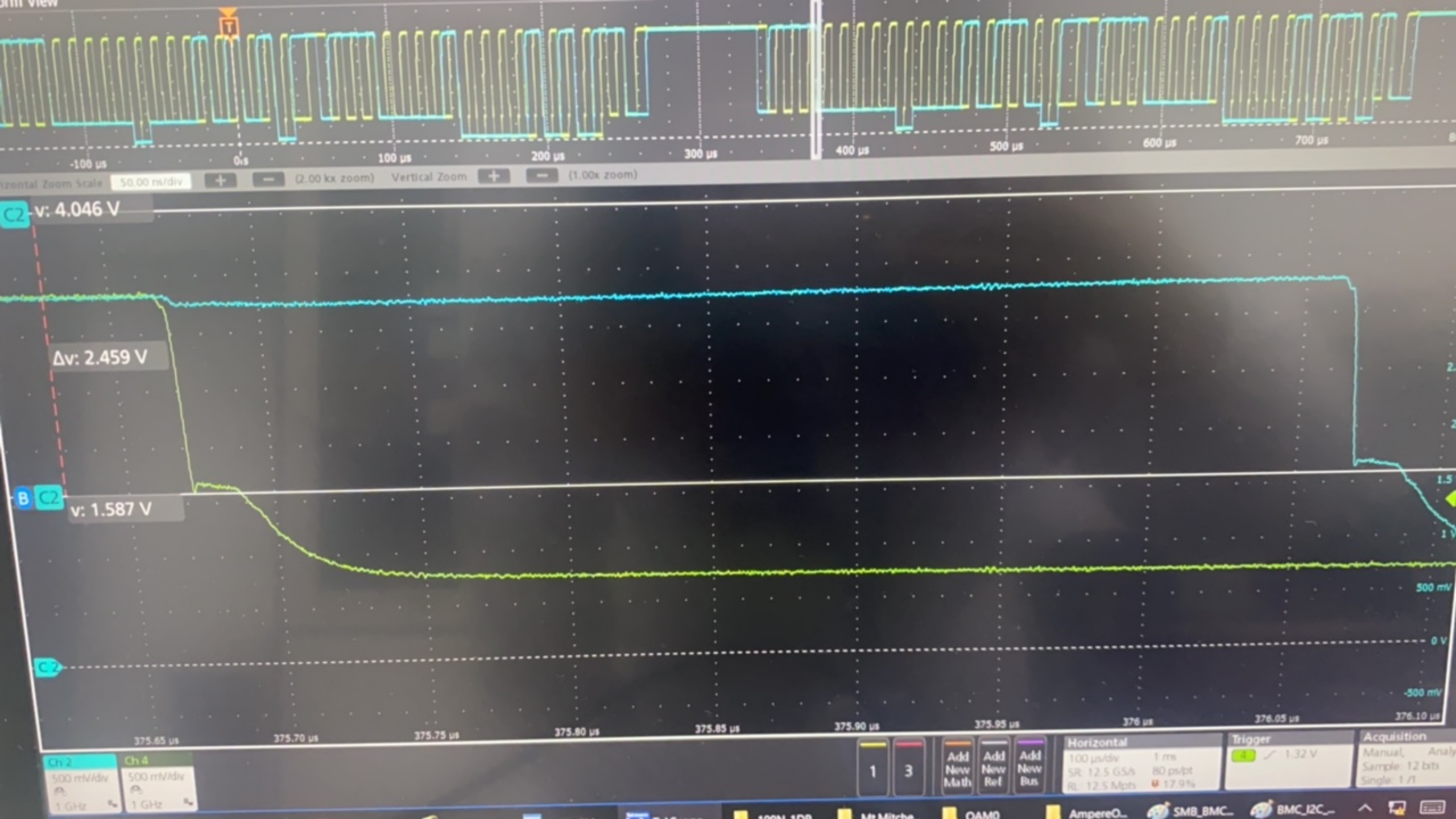

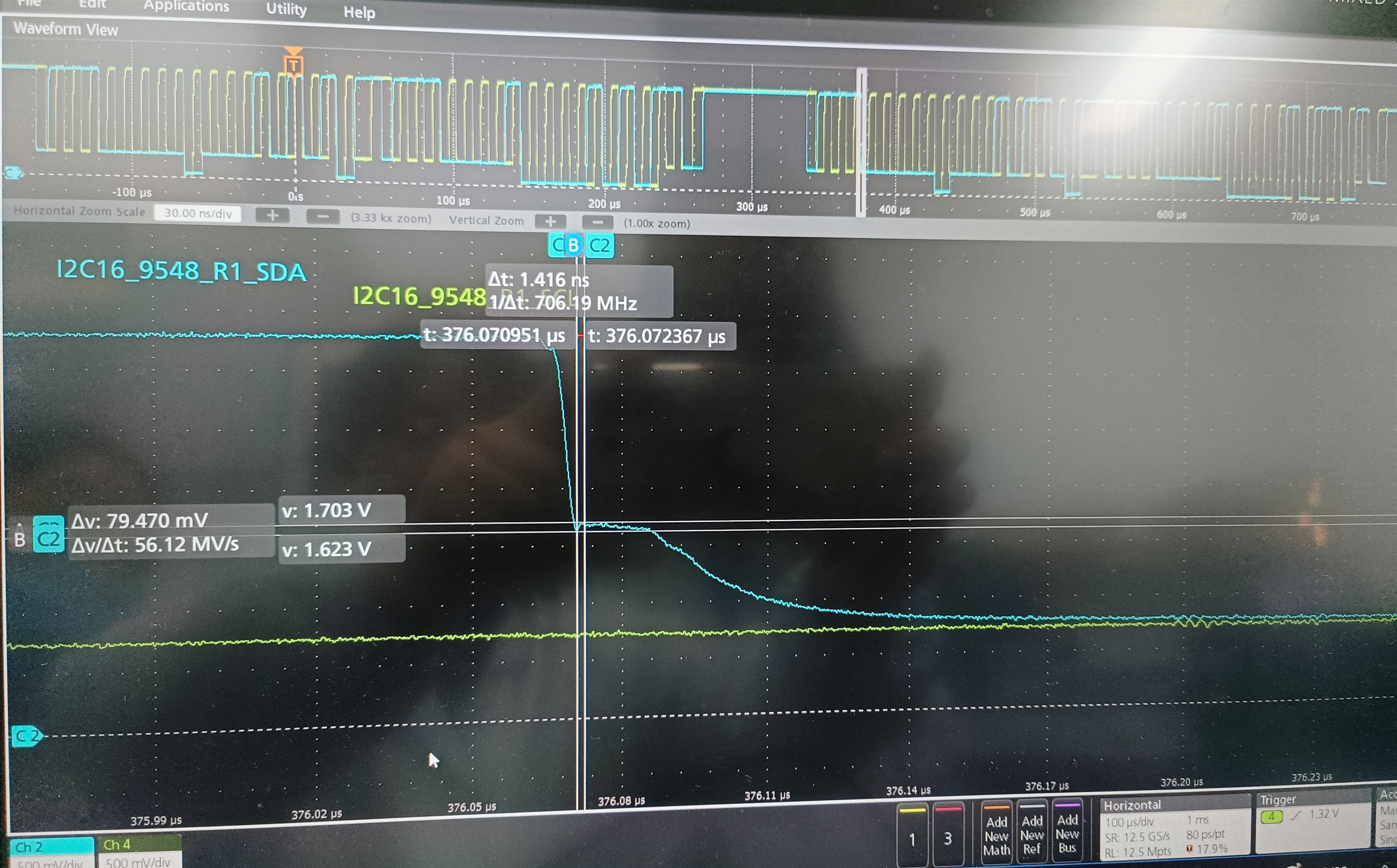

When TCA9548 connects to the master end I2C waveform write operation, it is found that there is a back channel on the falling edge of SCL/SDA (the test point is close to the chip end, the back channel occurs at 0.3VCC~0.7VCC, and the duration is about 1.416ns, see the attached waveform for details). This problem was not found when measuring the 8 I2C Slave terminals of TCA9548.

Please help confirm whether this problem is risky, and can you give any recommendation to avoid this issue?