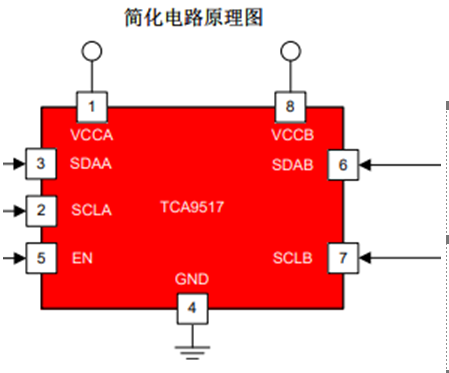

Part Number: TCA9517A

Other Parts Discussed in Thread: TCA9517

Hi team,

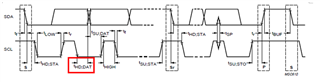

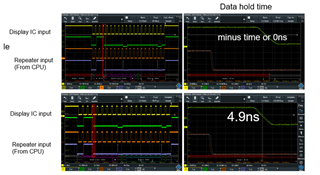

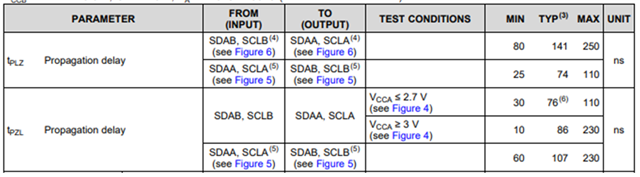

The datasheet shows the delay time of A to B or B to A, but if the interval between SDAA and SCLA during input is 5ns, can the interval between SDAB and SCLB at the output end also be maintained at 5ns?

Thanks

Lillian