Part Number: DS90UB941AS-Q1

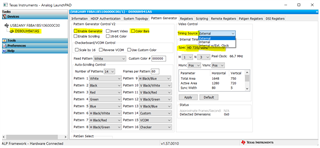

Other Parts Discussed in Thread: ALP

Hi,

I'm using a DS90UB941AS-Q1 sererializer combined with 2 DS90UB948 deserializer.

In this example the serializer is configured in "independent mode" and there's 1 JEIDA/HDMI adapter appended on the deserializer

on port0.

DSI input is configured to use Non-Burst Mode with Sync Pulses but I have a problem on the OLDI signal after the deserializtion.

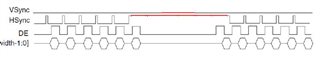

Problem is the VSync pulse signal is always low and HSync is moving high. They look like this:

Expected signals:

Inizializatoin sequence:

# initialize port 0 registers on serializer

18:22:52[936351250] ==> i2cset -y 5a820000.i2c 0x0c 0x1e 0x01

18:22:52[948901000] ==> i2cset -y 5a820000.i2c 0x0c 0x03 0xda

# overide the deserializer address to 0x20 on port 0

18:22:52[987897875] ==> i2cset -y 5a820000.i2c 0x2c 0x00 65

# initialize port 1 registers on serializer

18:22:52[998290750] ==> i2cset -y 5a820000.i2c 0x0c 0x1e 0x02

18:22:53[011161000] ==> i2cset -y 5a820000.i2c 0x0c 0x03 0xda

# overide the deserializer address to 0x30 on port 1

18:22:53[062667375] ==> i2cset -y 5a820000.i2c 0x2c 0x00 97

# set aliases on port 1

18:22:53[073215000] ==> i2cset -y 5a820000.i2c 0x0c 0x1e 0x1

18:22:53[086556250] ==> i2cset -y 5a820000.i2c 0x0c 0x07 148

18:22:53[098336500] ==> i2cset -y 5a820000.i2c 0x0c 0x08 74

18:22:53[111181625] ==> i2cset -y 5a820000.i2c 0x0c 0x70 128

18:22:53[124117250] ==> i2cset -y 5a820000.i2c 0x0c 0x77 66

18:22:53[137289250] ==> i2cset -y 5a820000.i2c 0x0c 0x71 48

18:22:53[149469000] ==> i2cset -y 5a820000.i2c 0x0c 0x78 68

# set aliases on port 2

18:22:53[162997500] ==> i2cset -y 5a820000.i2c 0x0c 0x1e 0x2

18:22:53[175168250] ==> i2cset -y 5a820000.i2c 0x0c 0x07 148

18:22:53[190164000] ==> i2cset -y 5a820000.i2c 0x0c 0x08 106

18:22:53[201068500] ==> i2cset -y 5a820000.i2c 0x0c 0x70 128

18:22:53[215402000] ==> i2cset -y 5a820000.i2c 0x0c 0x77 98

18:22:53[226420125] ==> i2cset -y 5a820000.i2c 0x0c 0x71 48

# finish initialization and start DSI

18:22:53[240726875] ==> i2cset -y 5a820000.i2c 0x0c 0x78 100

18:22:53[252157125] ==> i2cset -y 5a820000.i2c 0x0c 0x5b 0x05

18:22:53[266714500] ==> i2cset -y 5a820000.i2c 0x0c 0x12 0x02

18:22:53[277798875] ==> i2cset -y 5a820000.i2c 0x0c 0x1e 0x04

18:22:53[292367750] ==> i2cset -y 5a820000.i2c 0x0c 0x01 0x00

# initialize deserializer on port 0

18:22:53[315180125] ==> i2cset -y 5a820000.i2c 0x20 0x01 0x02

18:22:53[328120500] ==> i2cset -y 5a820000.i2c 0x20 0x05 0x9e

18:22:53[341034875] ==> i2cset -y 5a820000.i2c 0x20 0x26 0x32

18:22:53[353973750] ==> i2cset -y 5a820000.i2c 0x20 0x27 0x32

18:22:53[366440375] ==> i2cset -y 5a820000.i2c 0x20 0x49 0x02