Part Number: SN65DSI86

Other Parts Discussed in Thread: TEST2

Our project uses SN65DSI86 mipi to eDP, but now there is only backlight, no image, and no color bar display. What needs to be checked? Help guide and see where there may be problems.

Below are software and schematic diagrams to help check if they are correct.

VOID sn65dsi86_regInit(VOID)

{

sn65dsi86_write(SW_RST, 0x00);

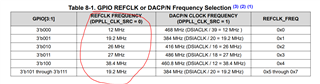

sn65dsi86_write(CLK_REG_0A, 0x03);// REFCLK_FREQ/DPPLL_CLK_SRC

sn65dsi86_write(CLK_REG_0D, 0x00);//songer

sn65dsi86_write(DSI_REG_10, 0x26);//songer

sn65dsi86_write(DSI_REG_11, 0x00);//songer

sn65dsi86_write(DSI_REG_12, 0x4c);//songer --------..note CHA_DSI_CLK_RANGE 0x50 400 < 405

sn65dsi86_write(DSI_REG_13, 0x4c); //chanel B

sn65dsi86_write(VIDEO_REG_20, 0x80);//songer,the length in pixels of the active horizontal line for Channel A

sn65dsi86_write(VIDEO_REG_21, 0x07);//songer,the length in pixels of the active horizontal line for Channel A

sn65dsi86_write(VIDEO_REG_22, 0x00); //chanel B

sn65dsi86_write(VIDEO_REG_23, 0x00); //Chanel B

sn65dsi86_write(VIDEO_REG_24, 0x38);// the vertical display size in lines for Channel A

sn65dsi86_write(VIDEO_REG_25, 0x04);// the vertical display size in lines for Channel A

sn65dsi86_write(VIDEO_REG_2C, 0x13);// CHA_HSYNC_PULSE_WIDTH_LOW -------...note

sn65dsi86_write(VIDEO_REG_2D, 0x00);// CHA_HSYNC_POLARITY/CHA_HSYNC_PULSE_WIDTH_HIGH ------...note

sn65dsi86_write(VIDEO_REG_30, 0x08);// CHA_VSYNC_PULSE_WIDTH_LOW -----..note

sn65dsi86_write(VIDEO_REG_31, 0x00);//CHA_VSYNC_POLARITY/CHA_VSYNC_PULSE_WIDTH_HIGH ----...note

sn65dsi86_write(VIDEO_REG_34, 0x14);//CHA_HORIZONTAL_BACK_PORCH

sn65dsi86_write(VIDEO_REG_36, 0x0b);//CHA_VERTICAL_BACK_PORCH

sn65dsi86_write(VIDEO_REG_38, 0x1e);//CHA_HORIZONTAL_FRONT_PORCH

sn65dsi86_write(VIDEO_REG_3A, 0x0c);//CHA_VERTICAL_FRONT_PORCH

sn65dsi86_write(VIDEO_REG_3C, 0x10); // songer COLOR_BAR_EN-->1

sn65dsi86_write(VIDEO_REG_3D, 0x00); // songer

sn65dsi86_write(VIDEO_REG_3E, 0x00); // songer

sn65dsi86_write(DP_SPEC_REG_5B, 0x00); // songer

sn65dsi86_write(LK_TRAIN_REG_93, 0x34);//songer

sn65dsi86_write(LK_TRAIN_REG_94, 0xe0);//songer

sn65dsi86_write(DP_SPEC_REG_5C, 0x01); // songer

sn65dsi86_write(DP_SPEC_REG_5A, 0x05);// default 0x05, IDLE pattern enable

sn65dsi86_write(CLK_REG_0D, 0x01);//songer pll_enable

MDP_OSAL_DELAYMS(10);

sn65dsi86_DebugDumpReg(CLK_REG_0D);

sn65dsi86_write(I2C_OVER_AUX_REG_64, 0x01);

sn65dsi86_write(I2C_OVER_AUX_REG_74, 0x00);

sn65dsi86_write(I2C_OVER_AUX_REG_75, 0x01);

sn65dsi86_write(I2C_OVER_AUX_REG_76, 0x0A);

sn65dsi86_write(I2C_OVER_AUX_REG_77, 0x01);

sn65dsi86_write(I2C_OVER_AUX_REG_78, 0x81);

MDP_OSAL_DELAYMS(10);

sn65dsi86_write(LK_TRAIN_REG_96, 0x0a);// 01 --> 0a

MDP_OSAL_DELAYMS(20);

sn65dsi86_write(DP_SPEC_REG_5A, 0x05);//songer temp

}