Hello Team,

I'd like to confirm about following points to do TDR test referring SLNA389a.

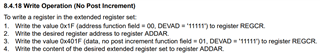

- Does following indirect access procedure correct?

There is some example for Read regarding indirect access but I couldn't found example for Write.

Write 0x8001 to register 0x1834- Write 0x1 to address 0xD

- Write 0x0834 to address 0xE

- Write 0x8001 to address 0xD

- Regarding testing TDR step 2, does this step mean we need change register setting based on [REGISTER READ/WRITE]? or it already applied at step for all registers?

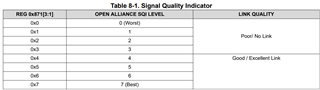

- Could you tell me how to select SQI setting according to the result of bit error rate?

We think there is 0 to 7 SQI setting and we need to select appropriate SQI setting regarding bit error rate.

We'd like to know about how to select appropriate SQI.

Best regards,

Kazuki Kuramochi