I am trying to understand the DP83TC813EVM-MC design https://www.ti.com/lit/ug/snvu825/snvu825.pdf?ts=1698444280751&ref_url=https%253A%252F%252Fwww.google.com%252F.

It is basically back to back PHYs (DP83TC813 and DP83867) connected through RGMII, and a micro-controller that can communicate to the PHYs over SMI. The back to back PHYs convert 100BASE-TX to 100BASE-T1.

I would like to implement the same design minus the microcontroller, and I want to make sure I understand the strapping. (I'm assuming the base design isn't dependent on PHYs being configured through SMI.)

As far as I know, to implement the back to back RGMII, the clock timing must be modified from default, which enables skews on both TX and RX clocks.

The 813 RGMII TX and RX clock skew is determined MAC[2:0], associated strapping pins are RX_D2-0. These are left open so MAC[2:0] = 111 (default). 111 translates to RGMII RX Internal Delay Mode active, TX Internal delay mode is not active.

I would expect the same configuration on the 867, but as far as I can tell both RGMII TX and RX clock skew is set to 2ns delay.

867 RGMII TX clock skew is determined by LED_2 and LED_1: neither are strapped, default = 000 = 2ns delay

867 RGMII RX Clock Skew is determined by GPIO_0,1: GPIO_0,1 which are both open. Default RGMII RX Clock Skew is 000 = 2ns delay

Shouldn't TX Clock Skew be set to 0?

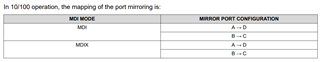

LED_0 is strapped to Mode three which disables SGMII, and enables port mirroring. What is the purpose of enabling port mirroring?

The configuration of LED_0 and LED_1 looks odd to me, but I don't work with Ethernet that much. Is this a standard configuration?

And a general auto-negotiate question: The 813 PHY is only capable of 100BASE-T1. How is this speed limitation communicated to the 867 PHY?

Any insight you can provide would be much appreciated!

Ryan