hi team,

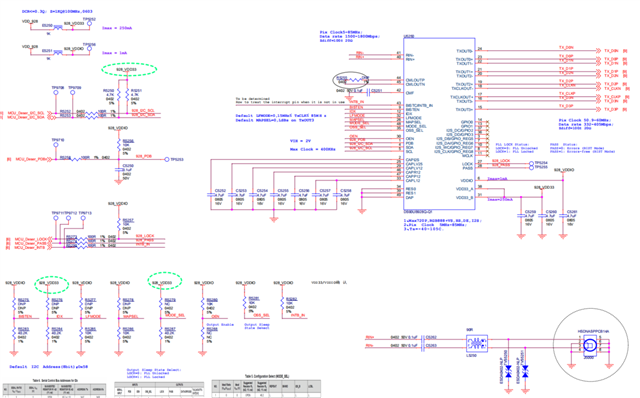

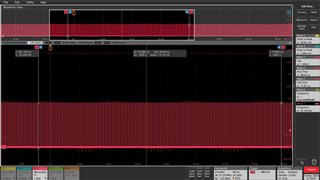

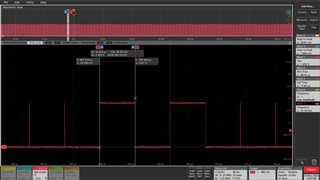

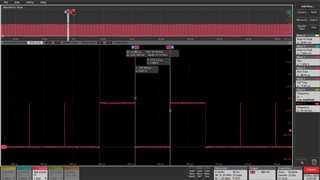

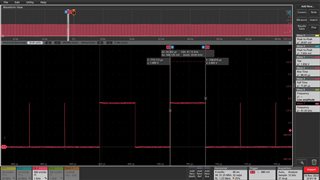

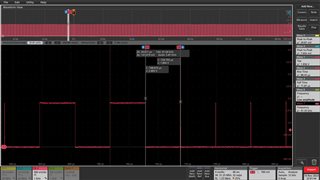

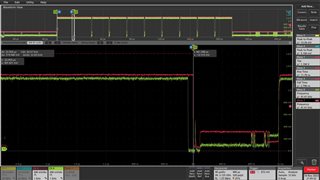

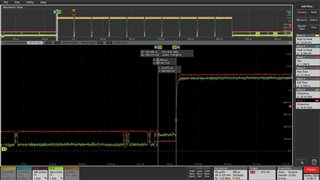

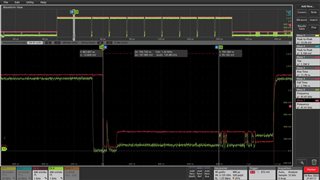

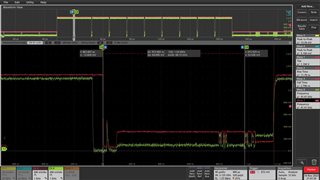

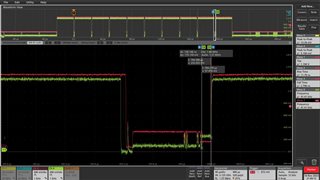

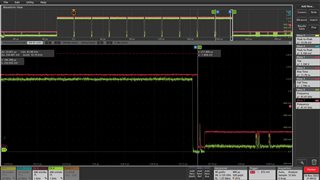

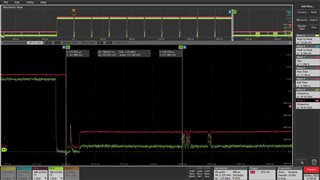

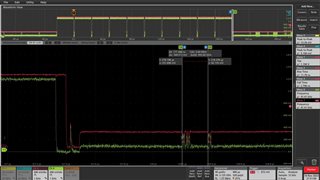

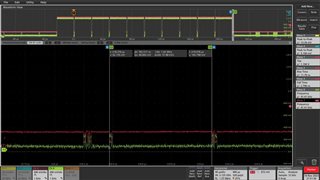

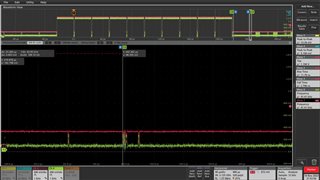

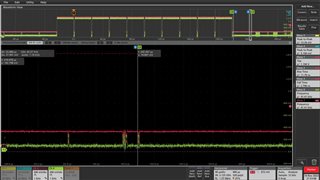

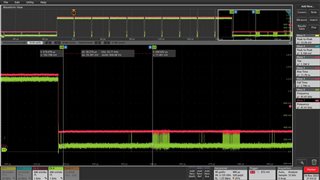

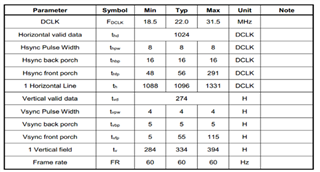

my customer use 941 pair with 928 and 926, now 926 can work normal, but 928 can't work normal, no video output.

back ground: the lock is no problem , I2C can work normal with 928, GPIO pass through can work normal

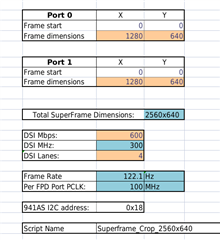

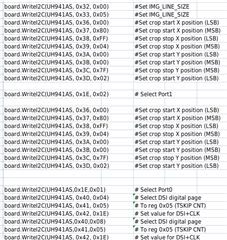

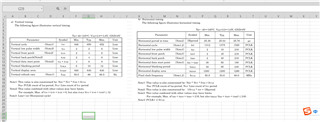

the 941 script config is as follow:

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/138/config_5F00_new_5F00_hud

could you help check the problem?