Part Number: DP83822I

If the DP83822I is used at high temperatures (over 75℃), communication errors will occur with certain ICs.

Please let me know the following four points regarding this operation.

①Would you please let me know the possible causes of the PHY internal register setting error occurring in the NG IC?

For example, is the reference voltage changing due to high temperature or some other reason?

②Are there any possible countermeasures?

③Would you please let me know if it have any concerns about communication errors other than register settings?

④If you have any other points to note when using DP83822I, please advise.

[Additional information]

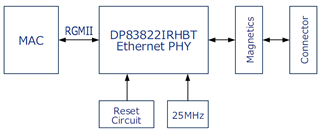

・The circuit configuration is based on the typical applications in the data sheet.

・There are differences in layout conditions between OK and NG ICs.

- OK: VIA ×9, There is a solid pattern on the back side.

- NG: VIA ×5, There is "not" a solid pattern on the back side.

・Even if the temperature is lowered after an abnormality occurs, the problem will not be improved.

Restarting after lowering the temperature will return to normal.

・After normal startup, no abnormality will occur even if the temperature is raised to 75℃ or higher.

If you restart after raising the temperature, it will fail.

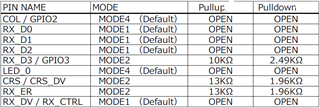

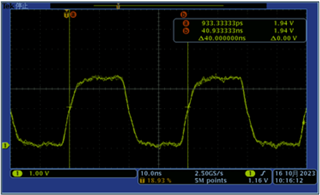

・25MHz clock is output from the [RX_D3/GPIO3] pin.

→ It is assumed that the shared pin was incorrectly set (extension register address 0x0462) during startup due to high temperature.

・There is no voltage fluctuation in BOOTSTRAP.

⇒We guess that the initial settings of the registers inside the PHY may be affected by something during startup at high temperatures, causing an error.

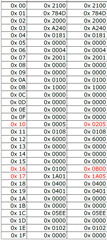

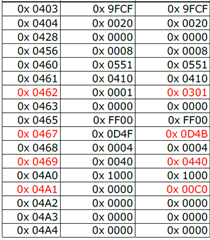

・The following is a comparison of registers for OK/NG. (Left: OK, right: NG)

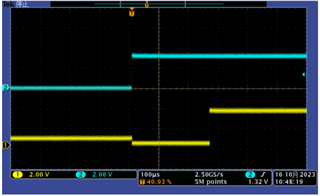

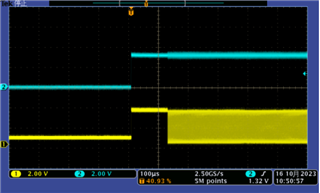

・The [RX_D3/GPIO3] waveform of OK/NG is shown below. (Left: OK and 0x0462 data is 0x0001, right: NG and 0x0642 data is 0x0301)

*Blue: PHY reset, Yellow: RX_D3/GPIO3

→Enlargement of NG waveform (25MHz output)

Best regards,

Satoshi