Part Number: DP83825EVM

Other Parts Discussed in Thread: USB-2-MDIO

I am trying to use a pair of DP83825EVM boards to add two 10baseT interfaces to an FPGA evaluation board. I have added zero-ohm resistors in the pads connecting RMII to J9 and connected J9 to suitable FPGA board ports, with the FPGA programmed as a rudimentary MAC. I have added a zero-ohm resistor at R46, removed R41, and wired a 50MHz clock from the FPGA board to J14 via twisted pair with 100-ohm impedance. I have removed R53 and R54 and wired FPGA IO to J10 to support register read/write from the FPGA. I have added a 2.49K pullup to CLKOUT to assign the RXDV pin function. I have added a zero-ohm resistor at R45 to set slave mode.

For initial testing I have provided a 10Mbps packet generator at the RMII RX port and am running near-end loopback testing. For this I have written the following registers:

Register 0x0000: 0x0100

Register 0x0017: 0x0081

Register 0x0016: 0x0001, 0x0002, 0x0004 for the various near-end loopback functions.

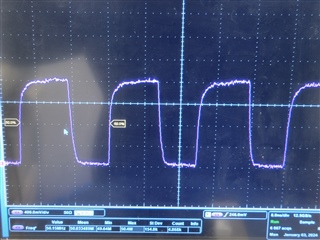

Applying test packets to the RMII RX port, I see RMII TX signals returned as follows:

0x0001: signal

0x0002: no signal

0x0004: no signal

So I am evidently losing loopback at the PCS output and onward. What might I be doing wrong?