Part Number: DP83822I

Hi Team,

Customer have extracted PHY logs for configuration Please let us know if the registers are properly set PFA.

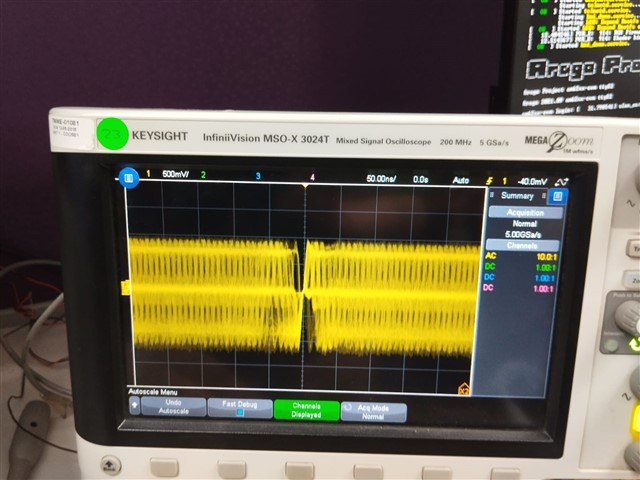

They have packet loss, operating in 100 Base TX/RX, PFA wave forms.

Any tweaking the internal registers for series termination will help ? Can you share your inputs & suggestions.

Tx.

Rx

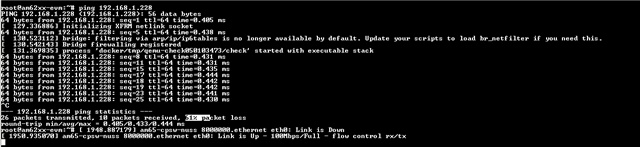

Ping Data

[2:41 PM] Illuru, Swapna root@am62xx-evm:~# reboot[ 31.798529] wlan_en: supplied by wlan_lten root@am62xx-evm:~# x=0; while [ $x -le 31 ]; do printf "Register 0x%02X = " $x ; phytool read eth0/1/$x $(( x++ )) ; done Register 0x00 = 0x3100 Register 0x01 = 0x786d Register 0x02 = 0x2000 Register 0x03 = 0xa240 Register 0x04 = 0x05e1 Register 0x05 = 0x4c41 Register 0x06 = 0x0007 Register 0x07 = 0x2001 Register 0x08 = 0000 Register 0x09 = 0000 Register 0x0A = 0x0100 Register 0x0B = 0x1000 Register 0x0C = 0000 Register 0x0D = 0x401f Register 0x0E = 0x1000 Register 0x0F = 0000 Register 0x10 = 0x0017 Register 0x11 = 0x0108 Register 0x12 = 0x2400 Register 0x13 = 0x2800 Register 0x14 = 0000 Register 0x15 = 0000 Register 0x16 = 0x0100 Register 0x17 = 0x1049 Register 0x18 = 0x0400 Register 0x19 = 0xb021 Register 0x1A = 0000 Register 0x1B = 0x007d Register 0x1C = 0x05ee Register 0x1D = 0000 Register 0x1E = 0x0002 Register 0x1F = 0000 [2:42 PM] Illuru, Swapna root@am62xx-evm:~# phytool read eth0/1/0x0461 0x786d root@am62xx-evm:~#

Regards, S Mathew.