Part Number: DP83867E

My customer is using DP83867E in their current design.

When they use DP83867, MDIO communication failure may occur after power-on (Linux will traverse addresses 0-31). When the communication fails, manually pull RESET_N low and then high, and MDIO communication returns to normal.

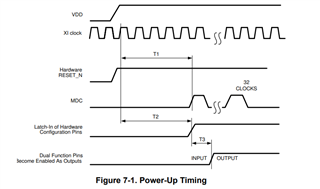

I suspect that the MDIO communication failure is related to the power on reset time duration. Please let us know the power on reset time duration and required power sequencing for the DP83867E PHY.

Currently, the PHY uses 3 supply modes (1.0V/2.5V/3.3V). The power-on reset timing diagram is as follows:

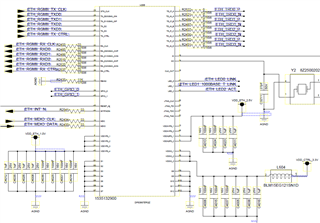

The customer application schematic diagram is as follows:

BR

Adrian