Hello,

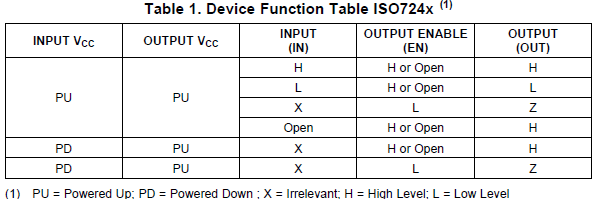

I would like to make sure output is "Z" or not while Vcc2 power rising/falling period.

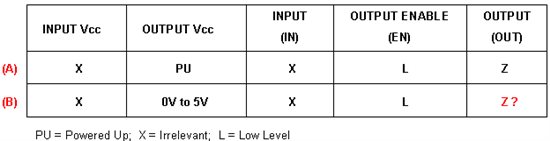

(1) While in Vcc2 (Output Vcc) power rising period (0V to 5V), output keeps "Z". (EN=Low, Input=Irrelevant) Is this correct?

(2) While in Vcc2 (Output Vcc) power falling period (5V to 0V), output keeps "Z". (EN=Low, Input=Irrelevant) Is this correct?

(3) If above are correct, I understand "output = Z" is independent of Vcc1 (Input Vcc). Is this correct?

I concern while in Vcc2 power rising/falling preiod, the output goes to unexpected state like "L" or "H". That means disable does not work during power rising/falling period.

Regards,

Hide