team, customer is testing out the timing they get on the RGMII, it doesnt seem to match our requirement completely, can you please comment ? customer is in cc

I have some other questions about the signal test. Please help confirm them.

Do you think it is acceptable or any risks? any other test methods to optimize?

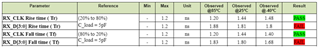

- RGMII RX_D[3:0] rising time and falling time. The test data is the worst values in the test. Each RX signal is NOK

2. The skew time of RGMII RX_D[3:0] from CLK is also NOK from the test result. the test data is the worst values in the test.