Part Number: SN65DSI86

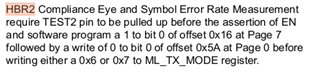

Other Parts Discussed in Thread: TEST2

Dear TI,

I did the following after TEST2 was pulled up.

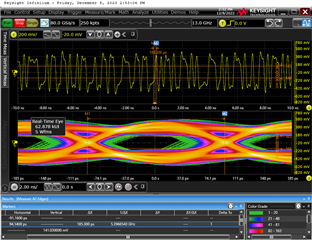

chose operation: [0]: HBR2 Compliance Eye Pattern [1]: Symbol Error Rate Measurement Pattern [2]: 80-bit Custom Pattern [3]: Other: Setting Reg [4]: Other: Read DPCD : 0 set reg: [0A] = 00000010 now reg: [0A] = 00000010 we will use refclk 1 set reg: [94] = 10000000 now reg: [94] = 10000000 set reg: [93] = 00110100 now reg: [93] = 00110100 set reg: [FF] = 00000111 now reg: [FF] = 00000111 set reg: [16] = 00000001 now reg: [16] = 00000001 set reg: [FF] = 00000000 now reg: [FF] = 00000000 set reg: [5A] = 00000100 now reg: [5A] = 00000101 set reg: [0D] = 00000001 now reg: [0D] = 00000001 set HBR2_COMPEYEPAT_LENGTH reg (260): 260 set reg: [98] = 00000001 now reg: [98] = 00000001 set reg: [97] = 00000100 now reg: [97] = 00000100 now ENCH_FRAME_PATT = SR BF BF SR or BS BF BF BS [0]: SR BF BF SR or BS BF BF BS [1]: SR CP CP SR or BS CP CP BS choose ENCH_FRAME_PATT (0): 0 set reg: [5B] = 00000000 now reg: [5B] = 00000000 [0] = Pre-emphasis level 0. [1] = Pre-emphasis level 1. [2] = Pre-emphasis level 2. [3] = Pre-emphasis level 3. set Pre-Emphasis Level (recommend 1): 0 set reg: [93] = 00110100 now reg: [93] = 00110100 [0] = Voltage swing level 0. [1] = Voltage swing level 1. [2] = Voltage swing level 2. [3] = Voltage swing level 3. set VOD level (recommend 1): 0 set reg: [94] = 10000000 now reg: [94] = 10000000 [0] = Post-Cursor2 Level 0 (0 dB) (Default) [2] = Post-Cursor2 Level 1 (0.92 dB) [4] = Post-Cursor2 Level 2 (1.94 dB) [6] = Post-Cursor2 Level 3 (3.10 dB). set post cursor2 (recommend 0): 0 set reg: [95] = 00000000 now reg: [95] = 00000000 set reg: [96] = 00000110 now reg: [96] = 00000110

now bridge reg is

00000000: 3638 4953 4420 2020 0200 8200 0001 0000 68ISD ........

00000010: 3e00 6500 0000 0000 0000 0000 0000 0000 >.e.............

00000020: 0000 0000 0000 0000 0000 0000 0000 0000 ................

00000030: 0000 0000 0000 0000 0000 0000 0000 0000 ................

00000040: 0100 0000 8000 0000 0000 0000 0000 0000 ................

00000050: 0000 0000 0000 2000 40e4 0500 1000 9000 ...... .@.......

00000060: a060 a400 0000 0000 0000 0000 0000 0000 .`..............

00000070: 0000 0000 0001 0301 9009 0000 0000 0000 ................

00000080: 0000 0000 0000 0000 001f 7cf0 c107 1f7c ..........|....|

00000090: f0c1 0734 8000 0604 0100 0000 0000 0000 ...4............

000000a0: 01ff ff00 0000 0000 0000 0000 0000 0000 ................

000000b0: 0478 acac 086c 9c9c 0c5c 5c5c 0c0c 0c0c .x...l...\\\....

000000c0: 3f3f 0f00 0000 0000 0000 0000 0000 0000 ??..............

000000d0: 0000 0000 0000 0000 0000 0000 0000 0000 ................

000000e0: 0000 0000 0000 0000 0000 0000 0000 0000 ................

000000f0: 0002 0000 0102 0000 0000 0000 0000 0000 ................

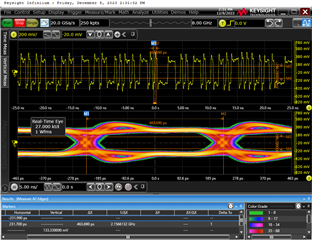

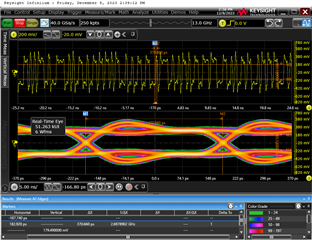

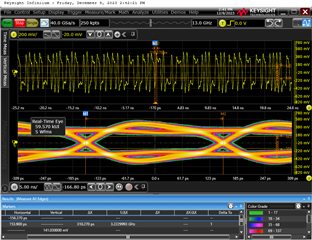

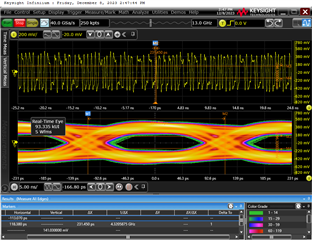

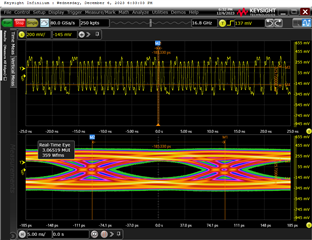

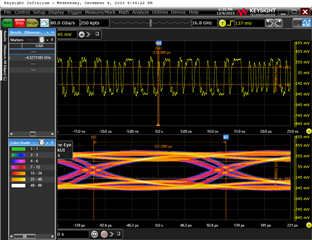

I set data rate hbr, but waveform is hbr2(5.4Gbps)

if i set data rate is 1.62Gbps, the waveform will be 4.32Gbps

I found that the waveform appeared when I was doing DP LOCK(0x0D), and I wasn't even sure if mode set to HBR2(0x96) worked because I didn't see a significant change。

I read the spec carefully and I couldn't find anything wrong with it