Part Number: DS90UB960-Q1

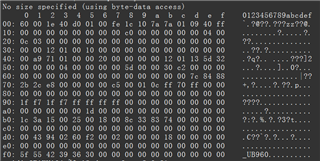

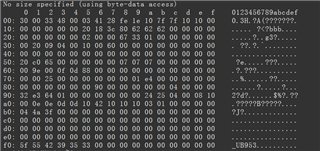

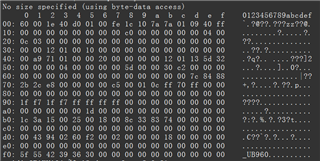

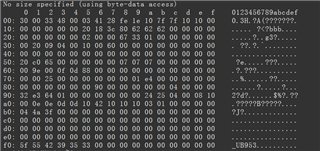

This is the ser dser registers. After start transmit, ub960 occur some CSI errors in register 0x7a, only connect ub953 one link port 0. Any config need fix to 953 or 960?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB960-Q1

This is the ser dser registers. After start transmit, ub960 occur some CSI errors in register 0x7a, only connect ub953 one link port 0. Any config need fix to 953 or 960?

Hello,

It appears that there are multiple errors being reported on the UB960 beyond CSI errors. Referencing register 0x4E, parity errors and BCC sequence error are seen on the link as well.

Referring to the UB960 register dump, the back channel frequency is incorrect for the intended mode. For CSI-2 synchronous mode, register 0x58[2:0] should be set to 110 for 50Mbps. This will correspond to the register 0x58 changing from 0x5D to 0x5E. The current setting is 0x58[2:0] = 101 which is a reserved register setting.

If the issue continues following this register change, would you be able to run MAP tool on the system from the UB960? Additionally, would you be able to share what cable and the length of cable which is being used to connect the UB953 to the UB960? Is this error consistent across all systems / is there a good system?

Best,

Zoe

When the TDA4 csi tx lane speed is reduced to below 410Mbps at 4 lanes, normal transmission can be achieved. but the ub953 up to 4 Data Lanes at 832 Mbps Per Each Lane. What factors will affect it? TDA4 config or ub953 congfig? Where setting the 953 lane speed?

Hi Yulong,

Was the back channel frequency changed in register 0x58? Register 0x58 on the 960 should be set to 0x5E. 0x5D is not a valid setting for the UB960 device.

The 953 is not configured to a specific lane speed. The configurations for the input CSI data to the 953 pertain to how many lanes are being used, and if the clock is in continuous or non-continuous mode in register 0x02.

Best,

Zoe