Part Number: DP83TC813R-Q1

Hello All,

The topic is about reading EthPhy Registers: TX_PKT_CNT, RX_PKT_CNT and especially RX_PKT_CNT_3

I have a couple of questions that would appreciate answers for them:

1- What is the proper way to read the registers TX_PKT_CNT_3 and RX_PKT_CNT_3?

2- There was a trial to read the registers RX_PKT_CNT_1 (0x063C)and RX_PKT_CNT_2 (0x063D) with the procedure of reading external registers

Step 1) write 0x1F to register 0xD

Step 2) write 0x063C to register 0xE

Step 3) write 0x401F to register 0xD

Step 4) read register 0xE

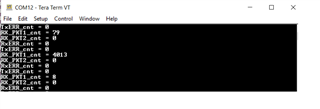

if I read the register again the register seems to reset and start from 0 again, as the screenshot attached shows the printed result from reading the RX_PKT_CNT_1 register.

What could be the reason of such response?

3- Could you provide an example on how to inject error on the Ethernet bus that would reflect in the registers RX_PKT_CNT_3 (0x063E) whether on HW or SW level?

and Thanks in advance

Best regards