Other Parts Discussed in Thread: SN65DSI86

HI,

I have a sn65dsi86 EVB connected to an im8mp EVB.

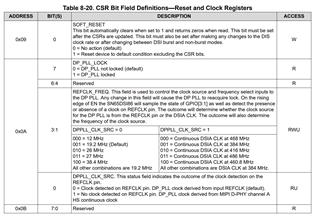

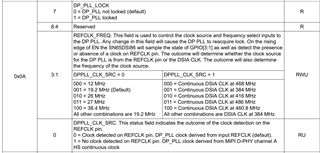

I'm trying to use the mipi_dsi clock (DPPLL_CLK_SRC = 1).

not getting any errors on boot but the display fails to init.

when using a "refclk" which I defined with a 27M clock the display and bridge work fine (no refclk on the target board so its not an option).

dts nodes:

mipi_dsi: mipi_dsi@32e60000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "fsl,imx8mp-mipi-dsim";

#clock-cells = <1>;

reg = <0x32e60000 0x10000>;

clocks = <&media_blk_ctrl IMX8MP_CLK_MEDIA_BLK_CTRL_MIPI_DSI_PCLK>,

<&media_blk_ctrl IMX8MP_CLK_MEDIA_BLK_CTRL_MIPI_DSI_CLKREF>,

<&clk IMX8MP_CLK_MEDIA_DISP1_PIX_ROOT>;

clock-names = "cfg", "pll-ref", "refclk";

assigned-clocks = <&clk IMX8MP_CLK_MEDIA_MIPI_PHY1_REF>;

assigned-clock-parents = <&clk IMX8MP_CLK_24M>;

assigned-clock-rates = <24000000>;

interrupts = <GIC_SPI 18 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&mipi_phy1_pd>;

status = "disabled";

port@0 {

dsim_from_lcdif: endpoint {

remote-endpoint = <&lcdif_to_dsim>;

};

};

};

sn65dsi86: sn65dsi86@2d {

compatible = "ti,sn65dsi86";

status = "okay";

reg = <0x2d>;

ti,dsi-lanes = <4>;

max,dsi-channel = <1>;

ti,dp-lanes = <4>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_mipi_dsi_en>;

gpio-controller;

#gpio-cells = <2>;

#pwm-cells = <1>;

enable-gpios = <&gpio1 8 GPIO_ACTIVE_HIGH>;

dsi-clocks;

clocks = <&clk IMX8MP_CLK_MEDIA_MIPI_PHY1_REF>;

//clocks = <&mipi_dsi 0>;

//clock-names = "refclk";

no-hpd;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

sn65dsi86_in: endpoint {

remote-endpoint = <&dsi0_out>;

};

};

};

};

};

please assist,

thanks!