Part Number: TLK10081

Other Parts Discussed in Thread: DP83869HM, DP83869

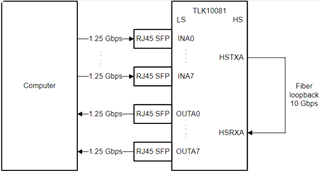

We need to connect 8 lines 1Gbps ETHERNET (SFP) through a 10 Gbps Fiber link.

We have choosen TLK10081 for this.

Is it posssible to get a full configuration for this. We have tested many configuration of HS/LS, PLL/VCO ...

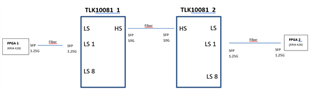

CLK_0 and CLK_1 are 10ppm TCXO (both side). CLK_0 is 125 MHZ, CLK_1 is 156.20 MHz.

It works with loopback (with fiber), but 8B/10B errors appear with fiber link (2 boards).

Best regards.