Hello,

I am writing to find out how TI deals with bugs on the silicon if they are not recognised in time. Are they recalled? Because we have found a Bug witch only can be explained by a bug on the Silicon.

Background: we are using the DP83826IRHBR (Ethernet PHY) in one of our designs. In the process, we came across a bug in one version that is related to the PHY. It concerns the strapping pin 0, which defines which duplex mode is used (full or half duplex).

The bug: PCB revision 1 negotiates the full duplex mode while the other revision 2 negotiates the half duplex mode, although the PHY is wired exactly the same. We have even swapped the PHY ICs between the two revisions with the result that rev1 now negotiates half duplex and rev2 uses full duplex.

The only reason we can think of at the moment is that there is a bug on the silicon of the PHY in one batch that reverses the polarity of the strapping pin0. More specifically, we believe that the PHY IC batch placed on rev1 has the described bug, because it does not behave as described in the data sheet for the strapping pin 0.

Print on PHY IC used in rev1: 826I TI 168 AEXJ G4 (see picture)

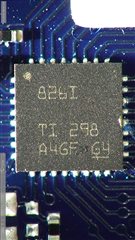

Print on PHY IC used in rev2: 826I TI 298 A4GF G4 (see attached picture)

I would be very happy about a possible explanation for this problem. If you need further information, I will be happy to provide them.

With kind regards,

Max Haymann