Other Parts Discussed in Thread: DP83826EVM

Hello.

I have a question about the DP83848 Auto-Negotiation feature.

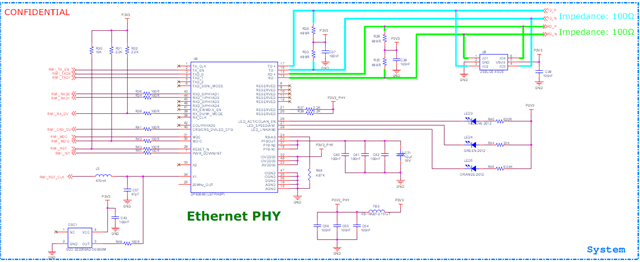

I've configured the circuit as shown in the attached picture, and I'm wondering if it is set up correctly for 10BASE-T, Half/Full-Duplex, 100BASE-T, Half/Full-Duplex.

Additionally, is it correct that the AN_EN, AN1, AN0 pins can be left floating while still using 10BASE-T, Half/Full-Duplex, 100BASE-T, Half/Full-Duplex?