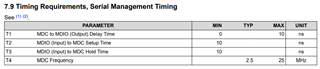

Other Parts Discussed in Thread: ALLIGATOR

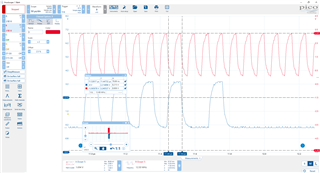

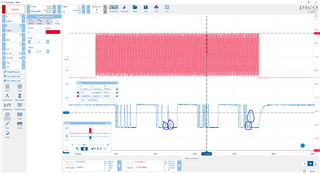

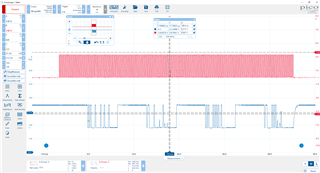

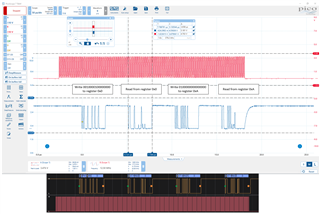

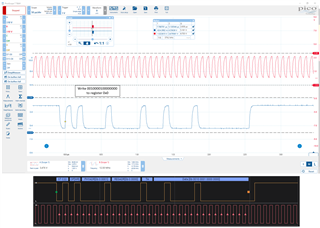

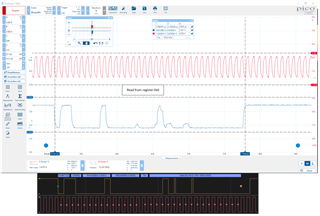

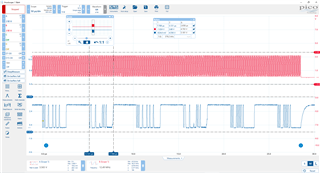

I'm using an FPGA to write to the PHY registers as I do with other PHYs.

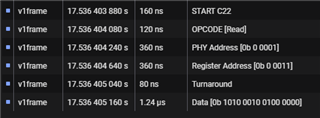

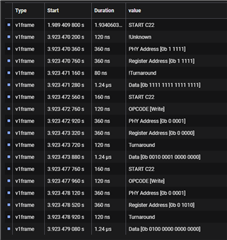

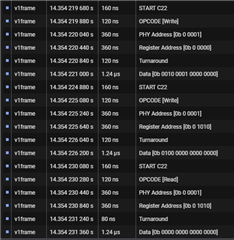

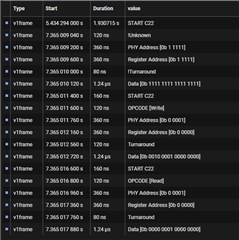

I send 32 ONEs as a preamble followed by:

SOF 0b01

OPCODE 0b01 (for write)

PHY ADDR 0b00001 (per datasheet 8.5.3)

REG ADDR 0x00 (BMCR)

I set bits 8 & 13 = 1 and bit 12 = 0

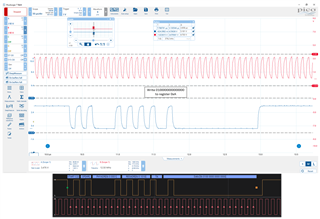

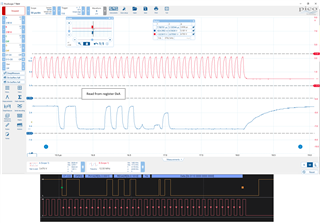

Then same SOF/OPCODE/PHYADDR but REG ADDR 0x0A with bit 14 = 1 (for FX enable)

I'm not being successful with this.

Is there something I'm missing?