Hi Team,

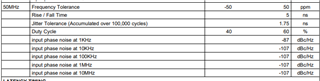

The customer enters the clock into the MAC and PHY(DP83825I) by distributing the crystal oscillator(50MHz).

Communication is unstable at this rate, but it will be improved by adding a damping resistor for each the MAC and PHY.

They are controlling the impedance.

Communication is unstable even if the clock buffer put instead of a damping resistor, so they can't help putting a damping resistor.

They think there is a root cause.

Can you think of anything that might have caused it?

They use at RMII Slave Mode.

Best Regards,