Part Number: TCAL9539

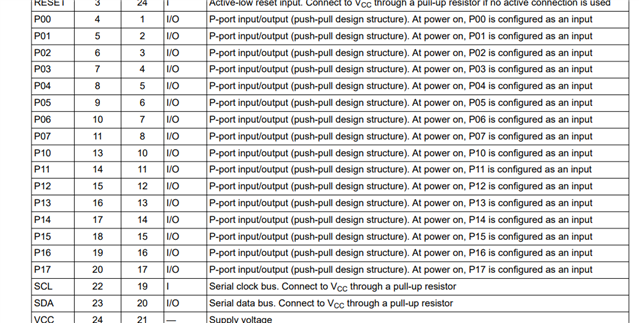

The customer want to configurate GPIO as open drain.

But I see it is push-pull design structure.

So whether it is available?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

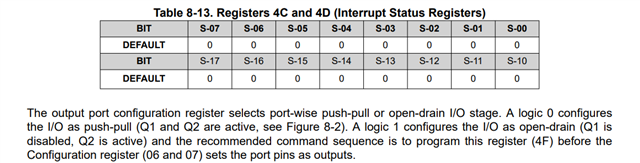

The description "push-pull design structure" means that the pin is capable of pulling high. But when a port is configured for open-drain I/O by setting its bit in the output port configuration register (4F), then its pins do not actually pull high.

Hi Fabio,

Clemens answered your question correctly. The pin description states that the design is push-pull architecture, but this doesn't mean that the push-pull design can be configured for open-drain by disabling the pull-up FET internal to the device.

Open-drain mode can be configured via register 0x4F.

Regards,

Tyler

Push-pull is set to registers46/47(Enable), 48/49(selection)

How can we control the behavior of each pin after setting it to open drain through 4F?

I did not see the open drain selection command from the datasheet.

Hi Fabio,

Unfortunately this is port-wise meaning that individual control of p-ports via push-pull / open-drain is not possible unless the whole port is configured.

There is a different approach around this. Please see how do conduct open-drain outputs via the output and configuration register and its implications in the FAQ here.

Regards,

Tyler