Hi Team,

I have a question about XIO2001.

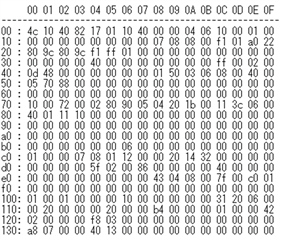

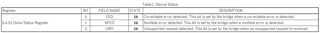

When I intentionally generated an Unsupport request (UR), some status changed in the device status. See Table 1 for device status.

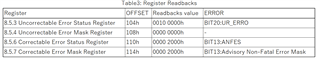

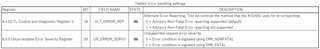

See Table 2 for the settings of "8.4.62 TL Control Diagnostic Register 0" and "8.5.5 Uncorrectable Error severity Register" related to error handling.

The PCIe standard is defined as follows.

"If the severity of the UR/CA error is non-fatal, the Completer must handle this case as an Advisory Non-Fatal Error.

A Completer with AER signals the non-fatal error (if enabled) by sending an ERR_COR Message. A Completer without AER sends no Error Message for this case."

In this case, please tell me why only correctable errors should be detected according to the standard, but nonfatal errors are also detected.

<Platform>

CPU:CORE i3-2310E (Sandy Bridge)

PCH:HM65 (Cougar Point)

Best Regards,

Wakumura