Other Parts Discussed in Thread: AM5K2E04

Hi,

As described in our former thread concerning this topic: "TUSB9261: USB repetitive RESET Burst during boot after Super Speed negotiation - Interface forum - Interface - TI E2E support forums"

we observed that the bridge doesn't behave the same way in our design integrating on the same PCB the Soc and the bridge, compared to an exploratory set up constituted of the K2E EVM board with the TUSB9261 demo board connected to the USB0 slot of the K2E EVM.

In our design random repetivive resets of the USB after SS training is observed, and none with the K2E EVM connected to TUSB9261 DEMO Board.

In some additional case we observed the USB bus to revert in SUSPEND mode until a new RESET occure, and this several consecutive times, inducing a long time for the SoC to discover devices on the BUS

Eye diagram aperture of USB3 SS diff signal seems correct in our design ( Keysight 33GHz scope used for this characterisation).

may the Bridge or the SoC Phi very sensitive to PS noise ?

We projects to replace one buck providing 1.1V to Bridge by a less noisy LDO.

Any ideas and suggestions from you are welcome.

Best regards

Fred

Bridge side ,with filter on his main PS

Bridge side ,with filter on his main PS

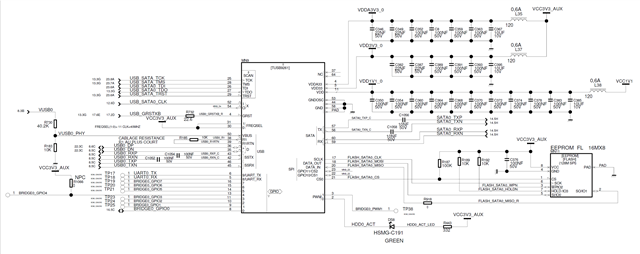

K2E side

K2E side