Hello.

We are using the component :DS90UB953-Q1 in our design .

So i am looking for the FPDIII  & Csi

& Csi  Eye diagrams and Eye Mask receiver standard details for signal integrity.

Eye diagrams and Eye Mask receiver standard details for signal integrity.

Regards.

Raneel.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello.

We are using the component :DS90UB953-Q1 in our design .

So i am looking for the FPDIII  & Csi

& Csi  Eye diagrams and Eye Mask receiver standard details for signal integrity.

Eye diagrams and Eye Mask receiver standard details for signal integrity.

Regards.

Raneel.

Hello Raneel,

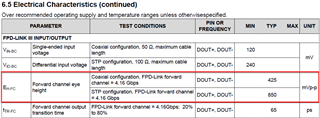

the forward channel eye diagram height can be found in the datasheet.

Also, there you can find the requirements for the incoming CSI-2 signal for AC and DC, HS and LP states.

Hello Raneel,

We do not recommend to characterize eye diagram/jitter for 953 since the only way that can be done is without the deserializer attached. When the deserializer is not attached, the SNR is not representative of what it would be in the actual FPD-Link application since the data transmission is bidirectional.

We recommend to use the Margin Analysis tool to check the system margin and we recommend characterizing the design physical layout s-parameters to ensure that those meet the required channel specifications for the device pair you are using as the way to qualify the design.

Please refer to the link below.

Hello Hamzeh Jaradat,

I am trying to do Link margin analysis of component DS90UB953 we don't have de serializer and we have installed ANALOG LAUNCH PAD,

I need support for the simulation, Can you please guide me for this with specific document or related video content.

or else I can share our PCB data to do analysis if you can help us.

we are expecting your support with this link margin analysis.

Regards

Raneel

PH: +918074662327

Hello Raneel,

Margin Analysis can only be run on a DES paired with a SER. This is to test the quality of the link between both devices and show how much margin you do have in your link. Unfortunately, there is no way to run this analysis on the SER only.

Just to clarify, are you trying to simulate the PCB using a 3D or 2.5D simulator for checking the signal Integrity performance of your board's design? If this is the case, then this is something we can't help you with. You may need to consult the Simulations software vendor for that.

Hi Hamzeh Jaradat

We have Simulated FPDIII serilazer Channel in Hyperlynx tool and Plotted IL & RL Losses. can you look into the attached graph.

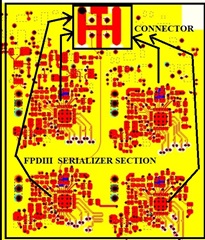

In below image we are using DS90UB953 serializer Ic to connector only. The Cable and de-serializer Ic is not used in our design scope.

So we are looking results till our layout board only.

Also let us know that we are on the same path.

.

Regards,

Raneel

Hello Raneel,

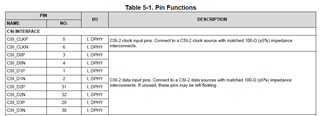

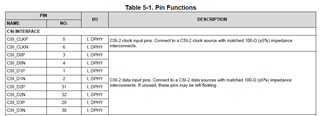

Our board level recommendations are as follow:

Frequency Insertion loss (dB)

1MHz -0.35

5MHz -0.35

10MHz -0.35

50MHz -0.35

100MHz -0.35

500MHz -0.35

1.0GHz -0.60

2.1GHz -1.20

-------------

Frequency Return Loss (dB)

1 - 100MHz -20

0.1 - 1GHz -12+8*log(F)

1 - 2.1GHz -12

To your measurements, I can see you have a big resonance at ~200MHz which violates our recommendations.

The only good measurement which is within our recommendations is Channel 3.

Hi Hamzeh Jaradat.

We have modified the layout and plotted the IL&RL losses attached here graph for FPDIII .

please have a look and confirmed is this meeting the requirement..

Regards.

Raneel