Hi

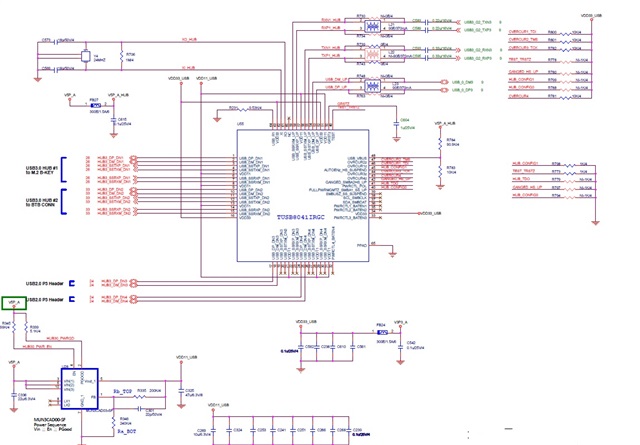

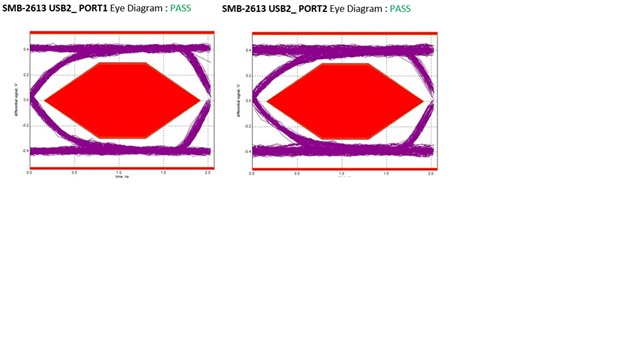

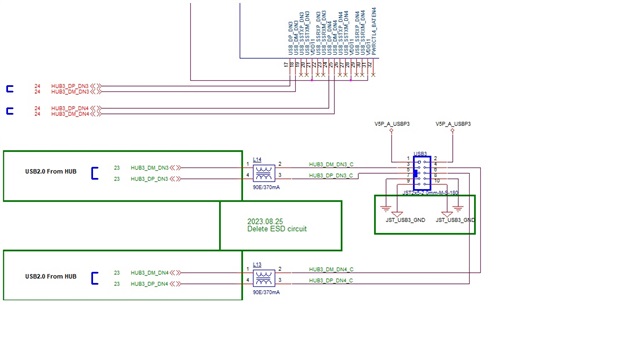

Customer is verifying USB2.0 Eye Pattern test Fail Is there anything that can be adjusted in this part?

The schematic is provided as attachment, the Fail port is located in USB3 (circuit diagram)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Gareth:

Customer can lower USB_R1 value to increase USB2 eye height. It failed on upstream port or downstream port?

how long is the trace length for that port?

Regards

Brian

Hi Gareth:

Customer can try 9k for R1. What is trace length for DP_UP and DM_UP?

Regards

Brian

Hi Brian

Thank you for your information. We will lower the USB_R1 resistance for verification. If there are any questions, we will contact you again.

It failed on upstream port right. Currently, there is no problem with the SoC native port verification eye pattern.

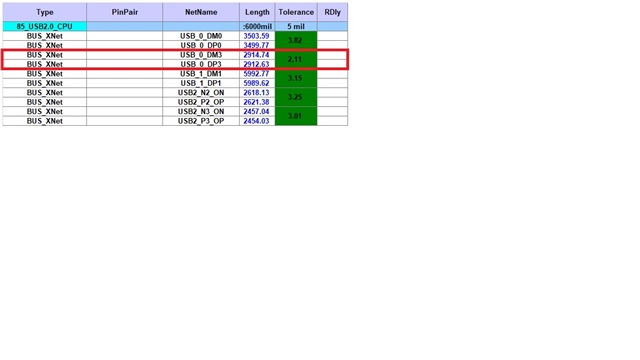

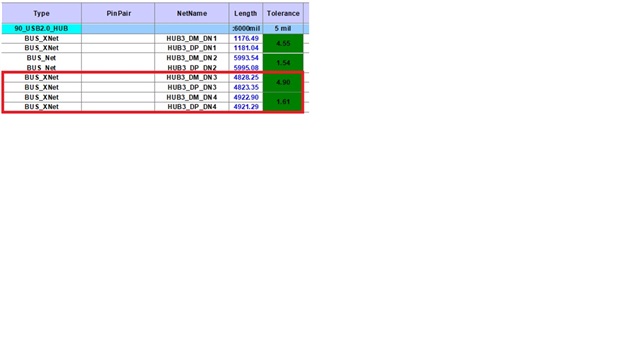

There should be no problem with the SoC to HUB section. The following is the SoC to HUB trace length table.

What is trace length for DP_UP and DM_UP?

Hi Gareth:

Normally if DP/DM trace length is over 4ch, USB2 HS eye diagram may not pass.

Is hub upstream port connected to SOC with trace only or with cable? I just wonder why need to test hub upstream port HS eye diagram if it is not connected to USB connector.

Regards

Brian