Part Number: TUSB8041

Other Parts Discussed in Thread: DRA829

I'm re-posting this issue in the interface forum to ask if the problem below is a problem for the Hub:

DRA829 is powered by 2x PMICs TPS65941213 and TPS65941111 just like J712E_EVM.

RESETSTATZ should be kept low until internal reset for the main domain is released. There is also a 10K pulldown on this signal.

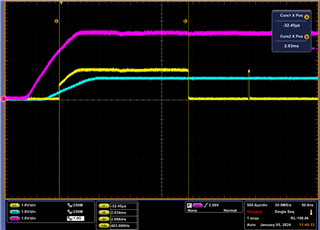

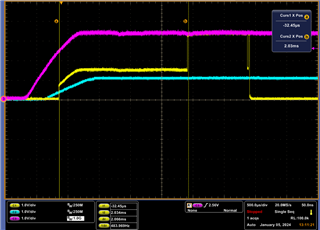

During power on VSYS_IO_3V3 (pink) ramps-up. RESETSTATZ (yellow) rises to ~1.5V during 2ms plus a minor glitch another ~1ms, before being pulled low and released after ~2s. This is without any FW loaded to DRA289.

With FW the behavior looks similar with another rise to 3v3 for ~1ms.

RESZETSTATZ is connected to as a reset signal to other peripherals there among USB HUB TUSB8041IRGCR just like Ti evaluation board.

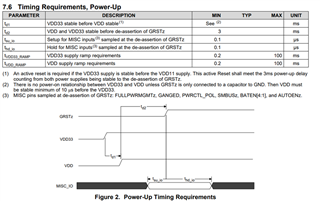

Power-up requirements for HUB are 3v3 followed by 1v1 rail, but the reset from RESETSTATZ will be outside of specifications, since it glitches before 3ms hold off (see below).

Is this behavior okay? Is there a suggested work around or alternative solution? Will it be a problem for the USB HUB? that is now operated outside its specifications.