Part Number: DS90UB960-Q1

Other Parts Discussed in Thread: DS90UB953-Q1, ,

Good afternoon,

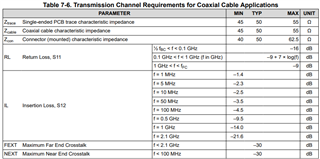

We're trialing a few PCB stack-ups for the best signal integrity to 4 x DS90UB953-Q1 devices (using RG-178 coaxial cable at 3 metre lengths) and appear to be struggling to identify which topology would be best suited to our application.

Could you recommend a suitable PCB stack-up for a design utilising 4 x SMB connectors please operating in synchronous mode at full data throughput (2.1Gbps, ~4.5GHz)?

We've trialed 2-layer and 4-layer PCBs with varying results. Our best design was a 2-layer PTFE design with a ZYF255DA core (DK = 2.55, Df = 0.0018) however, we would ideally like to move to (at least) a 4-layer design with an appropriate topology.

All signals on the current design are coplanar waveguide.

Many thanks,

Connor