Hi team,

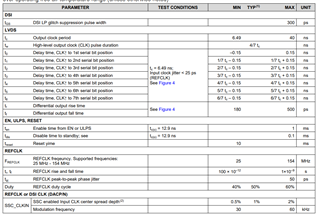

Our customer found that MIPI DSI CLK form SoC is unstable.

For example, if a 411MHz clock is required, there is a very low probability that the CLK becomes 409MHz due to instability.

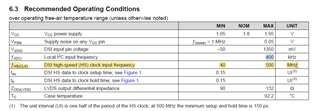

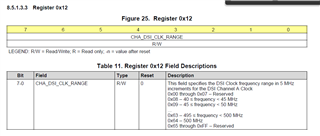

Register 0X12 is configured for a frequency range of 410MHz to 415MHz.

However, there is a very low probability that the DSI CLK becomes 409MHz. Besides replacing the clock source with REFCLK, are there any other solutions?

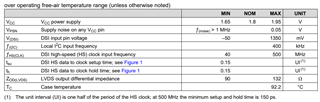

Another question: what are the stability requirements for the clock when PLL_EN is enabled?

Thanks

Xiaoxiang