Part Number: THVD8000

With the THVD8000 transceiver, what should be the observed behavior for bus contention? Are the observations deterministic for all combinations of dominant and recessive bit collisions?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: THVD8000

With the THVD8000 transceiver, what should be the observed behavior for bus contention? Are the observations deterministic for all combinations of dominant and recessive bit collisions?

Hi Rade,

So its actually a pretty complicated answer for a seemingly simple question unfortunately.

Ultimately the input thresholds are what guide what the output is at the "R" pin - regardless of bus state, the differential input voltage is what is the final determining factor.

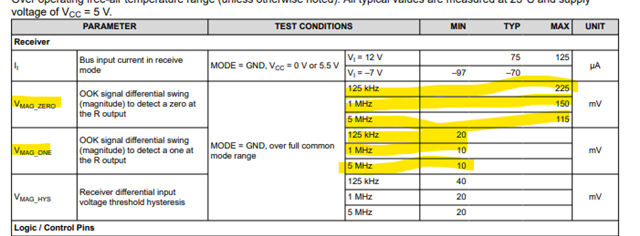

With these numbers in mind (which do vary based on modulation frequency selected) the next part of the analysis can begin.

typically you looking at about a 5 to 10 ohm output impedance of the driver when in a dominant state.

If multiple drivers are in the dominant state the bus will short out if at least one of the drivers out of phase - in this situation the bus will read a logic high as the differential voltage should be near 0 volts. However this can be complicated by the fact that for signals in phase with one another you could possibly have the bus read a logic low - generally the signal can be thought to be messy at this point. For quick blips (i.e. the devices are out of phase but not by full 180 degrees ) the internal bandpass filter may filter out the signal and still be read as a logic high. So multiple dominant drivers attempt to access the bus will result in bad data - but depending on how much the signals are out of phase will determine if the bus is "shorted" or not. If bus shorts out it will go high on output.

Now the recessive state is not driven that strongly - we estimate it, (its not directly specified in datasheet), to be about 60 ohms with a set point of 2.5V (really its half of VCC - but ultimately VCC = 5V is preferred for best performance) . If multiple devices try to access the bus in a recessive state the devices in receive mode will receive a logic high signal (VOD ~ 0V) - however if a driver in dominant mode tries to access the bus it will most likely override the recessive state on the bus due to the lower output impedance on the dominant mode driver. The more devices in recessive mode on the bus the less likely the driver is to override it. The biggest issue however is that this analysis only applies really on short bus applications - the longer the bus is the more likely it is that bus contention would result in VOD = 0V - but its not guaranteed.

Ultimately in general you can think of the situations as:

1. Multiple dominant transmissions - depends on phase of all signals but will result in bus being "shorted" and a high shown at active receiver outputs - ultimately the more out of phase a signal is the more likely it isn't read as a logic low signal. At the very least the the data signal would most likely fail any data integrity check done in the firmware if a short circuit occurred.

2. Multiple Recessive transmissions - will be read as a logic high by differential receivers

3. Mixed Dominant (1) and Recessive Transmissions - highly dependent on modulation frequency, cabling, bus distance, and loading. In a short bus setup the dominant is going to override the recessive state - however the recessive state impedance of the driver is much lower than the standard impedance of RS-485 device - so there is a higher amount of attenuation expected. This can create a situation in which the dominant doesn't override the recessive state. This is mostly a concern in applications that show the VOD at the last receiver is barely able to meet the VMAG_ZERO thresholds normally (not a lot of margin) could create situations where the recessive + dominant mix causes the dominant to dip too low and the receiver reads a logic high.

In general - Dominant will override recessive states in some cases but depending on actual bus setup it could lead to situations where that isn't necessarily true - but multiple dominant states trying to access the bus at the same time will result in the bus shorting out or having data corruption on the output data-stream that should be able to be caught by firmware. The best bet when thinking about bus contention with this device is to have a good firmware that can detect bad frames of information as the hardware can handle bus contention without being damaged but its less deterministic than it is for standard RS-485 due to its recessive output state.

Please let me know if you have any other questions!

Best,

Parker Dodson