Part Number: LMH0397

Hello,

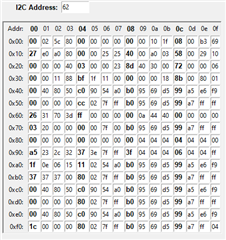

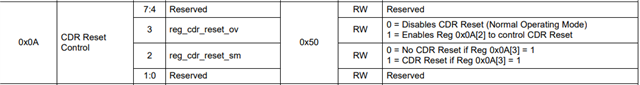

I have a question on the CDR reset control register bit 6 function on the LMH0397. We were trying to interface to a somewhat crappy HDMI-to-SDI converter and were having lock issues so we were trying to improve the signal integrity by adjusting EQ settings or bypassing and/or CDR bypass, etc without much luck. During checking out the CDR options, we inadvertently set bit 6 of register 0x0A (CDR reset) to '0' and the video cleaned up significantly. More so than any other options we tried. Can you tell me what that bit does? I provided a dump of the CTLE/CDR register space below (w/ 0x0A=0x10)

Thx - Tom