Part Number: SN75LVDS82

Other Parts Discussed in Thread: SN75LVDS83

Can SN75LVDS82 works with i.mx8mplus's LVDS output?

I was told the i.mx8mplus's LVDS1.8 output is 1.8V but SN75LVDS82's operation voltage is 3.3VDS.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN75LVDS82

Other Parts Discussed in Thread: SN75LVDS83

Can SN75LVDS82 works with i.mx8mplus's LVDS output?

I was told the i.mx8mplus's LVDS1.8 output is 1.8V but SN75LVDS82's operation voltage is 3.3VDS.

Hi George,

According to the Recommended Operating Conditions of the datasheet, the SN75LVDS82 requires a differential input voltage between 0.1V and 0.6V. The 1.8V coming from the i.mx8mplus does not follow the specifications, which is most likely leading to the white dots you are seeing.

Best,

Nikolas

"LVDS1.8" means that the pins are supplied by 1.8 V; the actual output voltages still are LVDS, i.e., generate ±350 mV over the 100 Ω termination.

Please show the schematic, and checke the LVDS waveforms with an oscilloscope.

Hi George,

Please refer to the i.mx8plus's datasheet and let me know what the output voltages are. We can then proceed forward with the issue you are seeing on the FPD-Link part.

White dots are a byproduct of something related to the power supplies (or noise on the power supplies). Please check that the power supplies are functioning correctly by probing the power rails.

Best,

Nikolas

1.

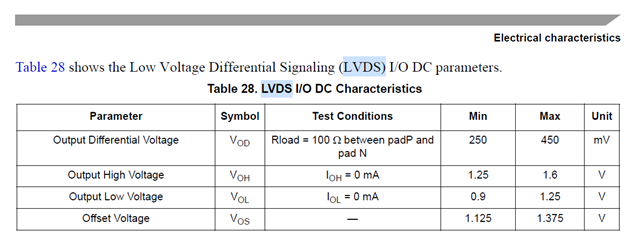

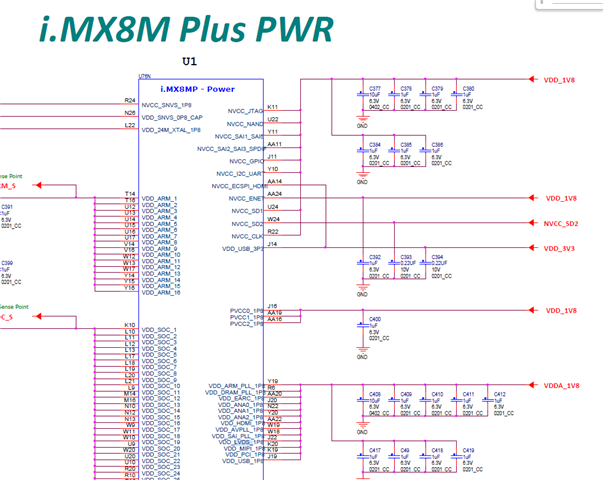

2. imx8mplus's spec shows it takes 1.8VDS input only:

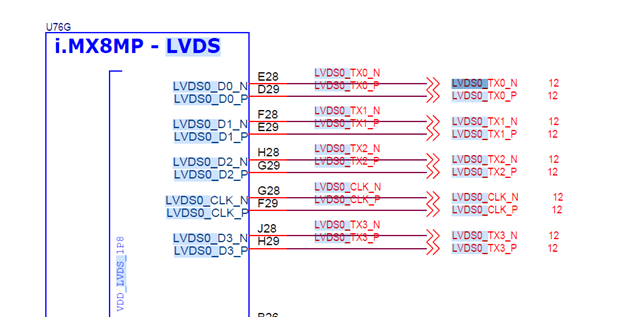

3. output from imx8mplus's LVDS

Regards,

George

The VIT+ and VIT− limits are the switching thresholds; these values specify that the differential input voltage must be at least 100 mV or −100 mV for the input to switch high or low.

The allowed range of differential input voltages is specified as |VID| in the recommended operating conditions; it allows up to ±600 mV. (All LVDS drivers output a nominal ±350 mV.)

Hello George,

Clemens' most recent response is accurate and for clarity's sake I am streamlining the flow of this thread.

Revisiting the white dots you are seeing on the output, white dots are sometimes a byproduct of something related to the power supplies (or noise on the power supplies). Please check that the power supplies are functioning correctly by probing the power rails.

Best,

Nikolas

When you move the video player window, do the dots move together with the window? If yes, then this problem definitely happens before the i.mx8 outputs the LVDS signal.

It appears that the white dots happen at some places with high contrast. This looks like a problem with the video decoder.

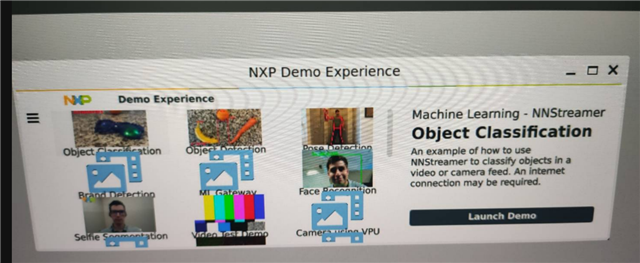

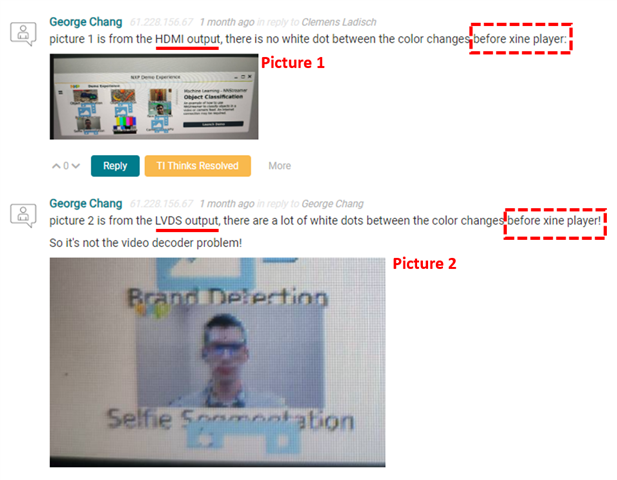

picture 1 is from the HDMI output, there is no white dot between the color changes before xine player:

picture 2 is from the LVDS output, there are a lot of white dots between the color changes before xine player!

So it's not the video decoder problem!

Hi George,

Have you probed the power rails to double check that the power supplies are functioning correctly?

Best,

Nikolas

Hello George,

Okay. Please let me know when you have any updates.

Best,

Nikolas

Hi George,

This device is not part of the FPD-Link portfolio and is therefore outside of my expertise. I would suggest posting a new E2E thread regarding this particular part (SN65LVDT100DR) for more assistance on constructing your level shifter

With that being said, though, are you not able to directly probe the power rails?

Best,

Nikolas

The power rails are OK, but the problem exists even with the level shift circuit using (SN65LVDT100DR)!

Hi George,

Could you please provide the schematic for the SN75LVDS82?

Best,

Nikolas

Hi Jack,

Let's take a step back and try and isolate to pinpoint which component in the system is causing the abnormality. It looks like the i.mx8mplus is capable of outputting both HDMI and LVDS. Could you please disconnect the SN75LVDS82 and instead connect the LVDS output of the i.mx8mplus to the display (i.mx8mplus --LVDS--> display) and see if the white dots persist? This will help identify if the issue lies with the SN75LVDS82, i.mx8mplus, or the display.

As an aside, could you please provide a full block diagram of the system, including what specifically is being output to the "xine player?"

Best,

Nikolas

Hi Nikolas,

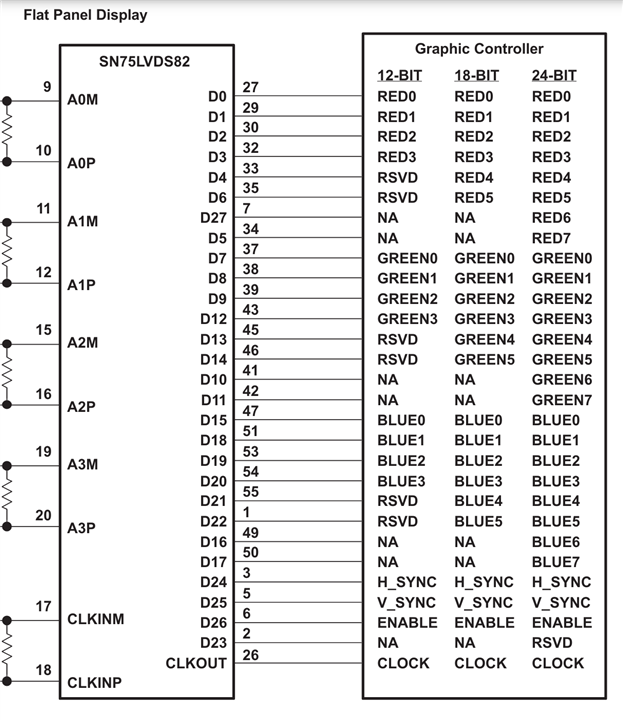

Excuse me! without SN75LVDS82 (LVDS receiver), how can you connect the LVDS output of i.mx8mplus to the TFT panel (it's 666 RGB interface)?

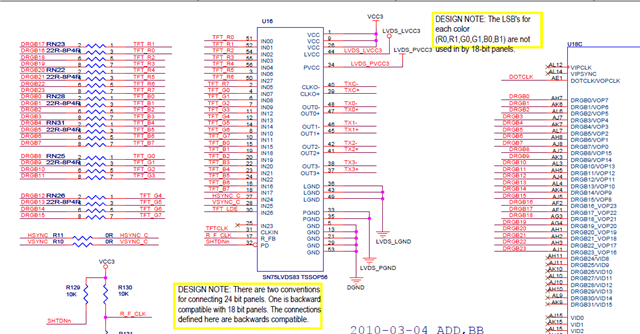

This LVDS receiver circuit works with AMD LX800 with SN75LVDS83 (LVDS transmitter) for our old product (with the same TFT panel) for 16 years already!

xine player is the AP to play video for Linux system.

Regards,

George

Hi George,

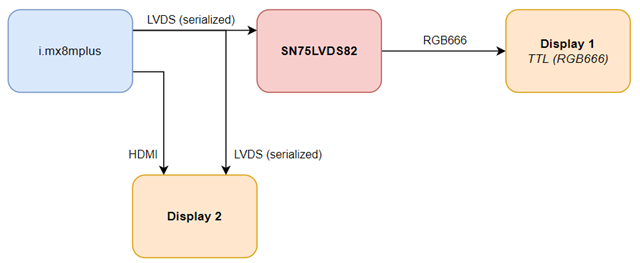

I think this emphasizes the need for a block diagram - I am not familiar with what components are at play in the system design is here. This was the first mention of a TTL (RGB666) panel in this thread, for example. Below is what I've gathered from the thread thus far - can you confirm that this is accurate, including with respect to where video data types are coming and going?

If this is in fact accurate, then I'd like to revisit these images from earlier in the thread:

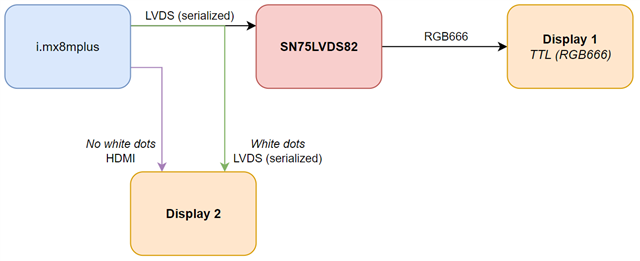

Given this information and proposed block diagram above, am I correct that in assuming that both picture 1 and picture 2 being "before xine player" means they are being fed to a display prior to the SN75LVDS82 component, as seen below to display 2, with the white dots being seen when following the green arrow, but not being seen when following the purple arrow?

If this is not accurate, please update the block diagram and let me know where the "HDMI output" and "LVDS output," both before the xine player, referred to in the previous responses are coming from and where they are going to.

Best,

Nikolas

Hi George,

Thank you for providing the updated block diagram. Please allow me 1-2 business days to discuss this further with my team.

Best,

Nikolas

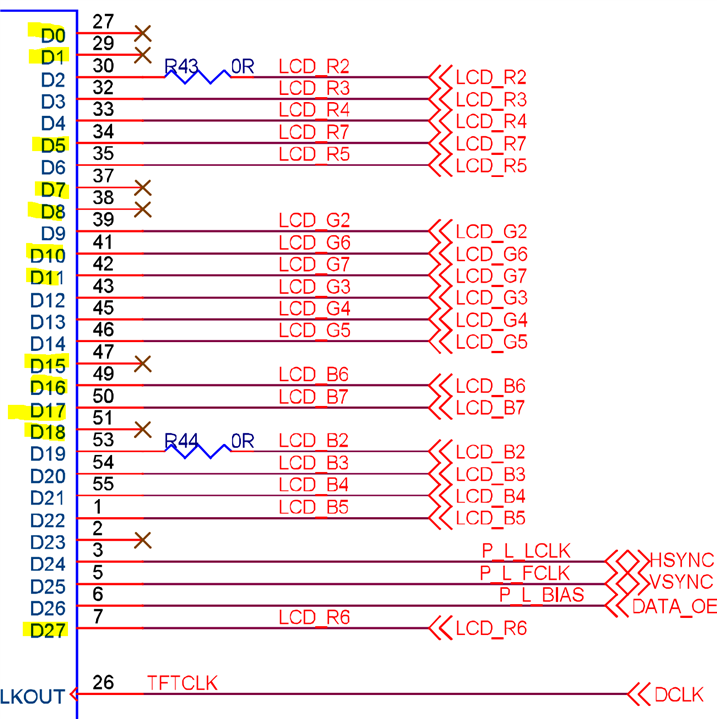

Hi George,

It looks like when the system transitioned from 24bit RGB to 18bit RGB, the data format on the SN75LVDS82's output was not appropriately adjusted to account for this change. More specifically, a certain bit-mapping is required on the SN75LVDS82 depending on how many bits are being used. Looking at the schematic, it seems as if the LVDS output of the SN75LVDS82 is still partially mapped for 24bit RGB instead of 18bit RGB, with mis-mapped pins highlighted in yellow. Please follow the datasheet's Typical Applications Diagram for 18bit RGB and adjust the schematic accordingly.

In addition, is there a specific reason why there are 0 Ohm resistors on some of the output pins and not all?

Best,

Nikolas

Hi Nikolas,

Because the previous generation used AMD LX800 (EOL soon), diagram as below, the panel was RGB 565, so that the LSB R0, R1, R2, G0, G1, B0, B1, B2 are all unconnected (which works fine for 16 years). The panel now used is RGB 666, so that R2 and B2 are connected using 0 ohm resistors.

Regards,

George

Hi George,

What datatype is the i.mx8plus outputting (i.e. RGB666, RGB888, etc.)?

Best,

Nikolas

Hi George,

The panel is expecting RGB666, correct? Looking at the schematic labelled "rec-7562_v10" in this thread, it looks like the panel has two inputs (R2 and B2) are grounded via two 0-Ohm resistors. Can you confirm if R41 and R42 are populated or depopulated?

Best,

Nikolas

Because the previous generation used AMD LX800 (EOL soon), diagram as below, the panel was RGB 565, so that the LSB R0, R1, R2, G0, G1, B0, B1, B2 are all unconnected (which works fine for 16 years). The panel now used is RGB 666, so that R2 and B2 are connected (0 ohm resistors R43 and R44 are populated, R41 and R42 are unpopulated)

Regards,

George

Hi George,

Thank you for the additional update. Two follow-up questions:

Best,

Nikolas

Hi Nikolas,

1. DCLK is 25.77MHz from SN75LVDS82 pin 26

2. We managed to solve this problem by setting the output clock from i.mx8mplus to 25MHz.

We didn't notice that before although we set it up as 25MHz but it automatically changed to 75MHz after booting. So that we changed the timing of the driver to fix at 25MHz.

Problem solved, thanks

Regards,

George

Hi George,

I am glad to hear that the issue is resolved. I am going to mark this thread as closed now.

Best,

Nikolas