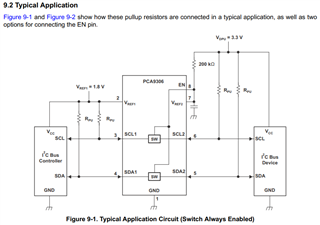

In the implementation shown in datasheet Figure 9-1, if the 3.3V supply is ON and the 1.8V supply is OFF, will SCL1 & SDA1 be high impedance?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.