Looking for datasheet clarification between release of reset until the Management Interface is active and any identified side effects if Management Interface comms occur too soon(<200ms wrt resert deassertion).

Question 1: Release of reset until the Management Interface interface is active.

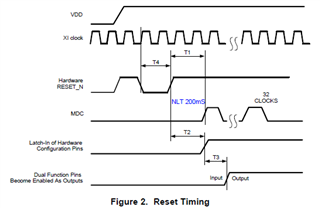

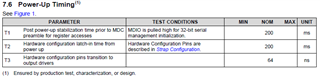

Section 7.6 states the time is 200mS (T1) from post power-up stabilization time prior to MDC preamble.

From Figure 1 (datasheet page 19) post power-stabilization would coincide with the release of the phy's hardware reset and that firmware (or software) should wait a minimum of 200ms prior to communicating through the MDC interface? Is an accurate interpretation? (ie. the time between H_RESET deassertion and initial Management Interface communications shall be no less than 200ms?)

Deducing that as a function of power-up stabilization, the 25MHz X1 crystal/clock is applied for 1uS (minimum 25 clocks, T4 timing minimum) prior to the release of reset and that all voltage rails have (at least) crossed the minimum input voltage threshold.

Question 2: If the minimum T1 time is not met (i.e. MDC starts too early), are there identified side effects? If figure 2 is correct, my assumption would be that the latch-in of the hardware configuration pins might not be reliably set but would appreciated your feedback.

Thanks in advance