Other Parts Discussed in Thread: DS160PR810, DS320PR1601, DS320PR410, DS160PR410, DS160PR1601

1. In the reference design, only the data signals of PCIe have been redriven, while the clk signals of PCIe have not undergone redrive. Is the attenuation of the refclk comparatively lower than that of the data signals, such that it can be used normally even if not processed as in the reference design? Additionally, can the refclk be enhanced with a redrive card like the data signals are?

2. Can a single DS160PR810 handle two port X4 width PCIe links simultaneously, thereby utilizing all 8 LANs effectively?

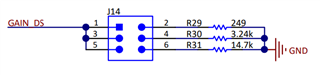

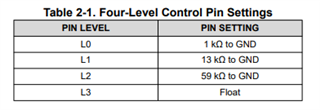

3.In the reference design, why is the ground resistance of J14 different from what is described in Table 2-1?