Part Number: TLIN1021A-Q1

Hi Expert,

We have some questions related to LIN. Please help check.

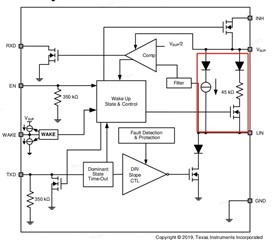

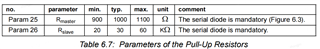

1. The following figure is the internal block diagram of TLIN1021. As shown in the red box, the pull-up resistor used by TLIN1021 is 45KΩ. The pull-up resistor typ value of the slave end specified in the LIN protocol is 30KΩ. What is the reason why the typ value is set larger than that of the LIN protocol? We believe that larger pull-up resistors will affect the driving ability of the LIN bus and have an impact on the signal under multiple loads.

2. Related to the above question, what is the function of the current source on the left side of the pull-up resistor in the red box?

3. The LIN protocol stipulates that the length of the LIN bus shall not exceed 40m. How is this bus length calculated? Does it include the length of the bus and each node branch?

4. How to understand the four specified Duty cycles? Are these different duty cycle related to different working voltages? Are these required to be covered during testing? When performing hardware testing, what timing indicators must be tested and verified?

Thanks!

Ethan Wen