Other Parts Discussed in Thread: DP83869HM, DP83869, TLK10022, TLK10034, TLK10232, TLK10031

Hi, I'm working on an application that aggregates 2 gigabit ethernet into a single high-speed link bidirectionally like this:

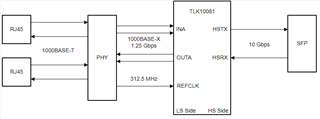

(LS) 2 x RJ45 (1000/100/10BASE-T) MDI <---> PHY <---> 2 x 1.25 Gbps (SGMII) <---> 10 Gbps HS Link (Fiber/Copper/wireless) <---> 2 x 1.25 Gbps (SGMII) <--> PHY <---> 2 x RJ45 (1000/100/10BASE-T) (LS)

My questions are:

1) Is it a suitable diagram if i do not use any media converters like for copper to fiber? I don't care about the protocol transferred in High-speed transmission channel.

2) If I use a PHY device SGMII with Reference Clock (625 mhz) ( to support Synchronous Ethernet, is it suitable for synchronous clocking of the Low Speed Side of the TLK10081 like diagram BELOW?

Or, I'm thinking about using multiple port PHY device which has more than one SGMII outputs. If synchronization is satisfied by the internal clocking of PHY, is it suitable for TLK10081?

3) Can I use 8 LS input from directly 4 twisted pair of Gbit Ethernet x 2 (from 2 x RJ45) and use bit interleave mode for raw data (1000Mbps / 4 = 250 Mbps per pair)? Actually, I don't care about the data rate here, It can be 100base-t or something else, wondering if I can use raw ethernet data as input of TLK10081 or something else.

Hope that my questions are clear, thank you for your support,

Ece