Part Number: DP83869HM

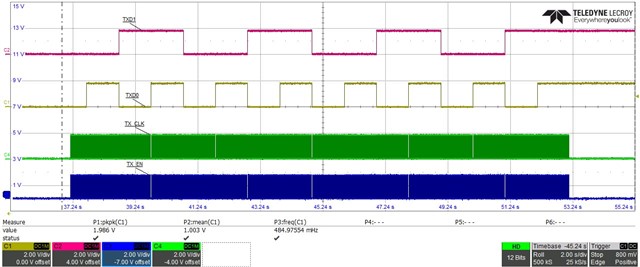

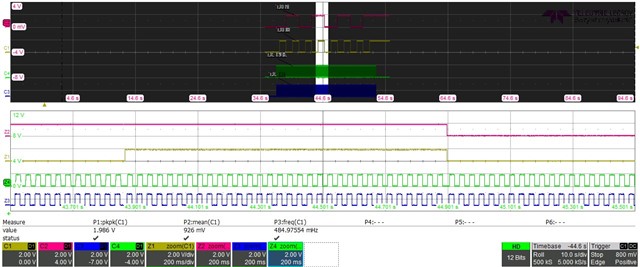

I am currently trying to do some functional testing of the PHY to verify the RGMII connection to an FPGA. I am using the JTAG Boundary scan cells to read and write signals. I am using Boundary scan instead of programming the FPGA itself, because we want to use JTAG in our production verification, without having to program the FPGA. This means That I am running at very low frequencies, the TX_CLK runs at arround 33Hz. So possibly here lie some of the issues, but the example projects we have gotten from JTAG for other PHYs use the same frequency and do not have any issues, so I have assumed these signals to be correct for this application, but have concluede some scope images anyway. Rx lines are not shown, but do not show any activity.

Since I am unable to get anything on the RX lines at all, it leads me to believe that I have not configured the registers correctly to get it into MII loopback mode. Following the datasheet I have come to the following configuration:

Register Name Value

0xFE LOOPCR 0xE720 (as specified by the datasheet, but not further specified what setting this register does)

0x0 BMCR 0x4100 (MII_LOOPBACK Enabled, Atonegotiation off, and still full duplex)

0x16 BIST 0x4 (tried with and without setting this register, datasheet implies that it would only be necessary when in 100Base-TX mode, but tried anyway)

I've read back these registers, so I am sure that they are set like I've mentioned them here. Is there something obvious that I am missing?