DS320PR810 Lane Configration question

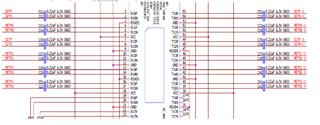

I make a board used two DS320PR810 .

I put singnal of PHY first then , Lane configration is blelow.

Host DS320PR810(No1) DS320PR810(No2)

Lane1 Lane2 Lane5

Lane2 Lane4 Lane3

Lane3 Lane5 Lane2

Lane4 Lane6 Lane1

Does your devices work?

if your device doesn't work , does it work by modyfied show below?

Host DS320PR810(No1) DS320PR810(No2)

Lane1 Lane3(change) Lane4(change)

Lane2 Lane4 Lane3

Lane3 Lane5 Lane2

Lane4 Lane6 Lane1