Other Parts Discussed in Thread: DP83822I

Hello,

We are developing prototype whose ethernet connection is based on the DP83867IRRGZR.

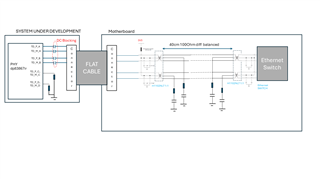

The solution needs to be plugged to a rather unconventional system that has been designed with Phy (DP83822i) and magnetics split in two boards.

In the original system, the differential pair is generated in the board to be plugged and is sent to the main board via a dedicated flat cable in violation of every recommendation from TI.

The magnetics CT in the mother board is connected to a positive supply as it is requested by DP83822i. This is a problem for the DP83867IRRGZR which works in voltage mode.

A solution we've been talking about is to break the DC-path between the PHY and the transformer with unpolarized capacitors. Do you believe this can work?

Which value would you suggest for the capacitors?

Best Regards,

GZ