Part Number: DP83867CR

Hello team,

This thread is regarding this.

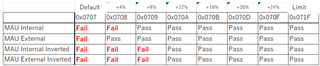

As advised, the customer changed the test from 10Base-T to 10Base-Te and conducted a MAU test. As a result, the customer confirmed that the pattern overlaps with the mask. Could you please consider the solution as I attach the test results?

Ethernet Test_10base-Te_25032024.pdf

Regards,

Masakazu Adachi