Part Number: SN65DSI84

Other Parts Discussed in Thread: SN65DSI85

Hello,

We are using SN65DSI84 to convert from DSI to LVDS on our custom i.MX8MP board.

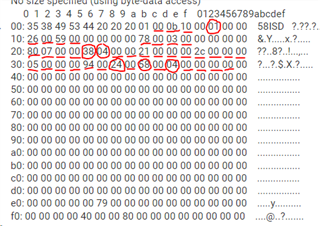

We used the DSI tunner to obtain the values for CSR registers, Our requirement is single channel DSI to single link LVDS (with 1 Clock & 4 Data lane), 24 BPP, and RGB888 Format. Instead of pannel we have an FPGA, i.MX8MP -> SN65DSI84 -> FPGA.

The issue is blank screen with some noise and we notice that LVDS clock frequency is very low (12.4MHz) when probed using oscilloscope instead of (actual 74.5MHz) and the PLL status bit in register 0x0A keeps changing, increasing the wait time for PLL lock did not work.

root@:~$ i2cget -f -y 1 0x2c 0x0a

0x8b

root@:~$ i2cget -f -y 1 0x2c 0x0a

0x0b

root@:~$ i2cget -f -y 1 0x2c 0x0a

0x8b

root@:~$ i2cget -f -y 1 0x2c 0x0a

0x0b

We need 1920x1080 resolution at 30 FPS at the bridge output & the timing info are mentioned below and also please find the attached screenshot of DSI tunner inputs.

Horizontal Timings:

HFP 88

HPW 44,

HBP 148,

Blanking Total 280,

Total Pixels 2200

Vertical Timings:

VFP 4,

VPW 5,

VBP 36,

Blanking Total 45

Total Lines 1125

Thanks & regards,

Shaswath