Other Parts Discussed in Thread: AM62A7,

Dear TI experts,

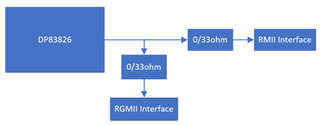

My customer drew their schematic with DP83826E, which is connected to AM62A7.

Could you review this schematic first?

And here are more questions.

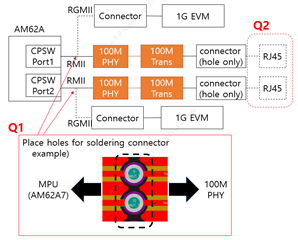

1-1. They want to insert additional connector to connect EVM which can support RGMII (1Gbps) interface.

In this case, Can my customer make through hole on signal line of RMII? (the point which refers red arrow in Q1.)

1-2. If yes for question 1, Should my customer disconnect RMII interface if they connect RGMII interface instead?

1-3. Should my customer make a routing with 100ohm differential routing or same length routing (or both?) between AM62A7 and DP83826E?

2. My customer will use the ethernet cable like the picture below.

(53261-0871 is the connector for this 1*8 array cable.)

Before production, Can my customer use another RJ45 connector only for the test? this RJ45 connector will be removed before production.

Is it okay to draw schematic like the pdf file above? or Do you have better solution for thest?

Best regards,

Chase