Part Number: PCA9539

Other Parts Discussed in Thread: TCA9617B

Hi,

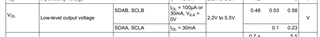

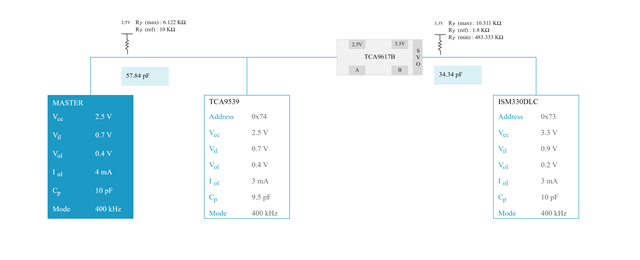

I am testing a board and see some signal integrity issues with I2C bus. In our design, we use FPGA as I2C master with open-drain on I2C bus. we have PCA9539 for IO expansion. we also have TCA9617B as I2C driver for a motion sensor with 2meters cable.

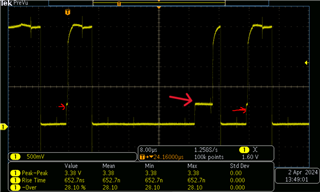

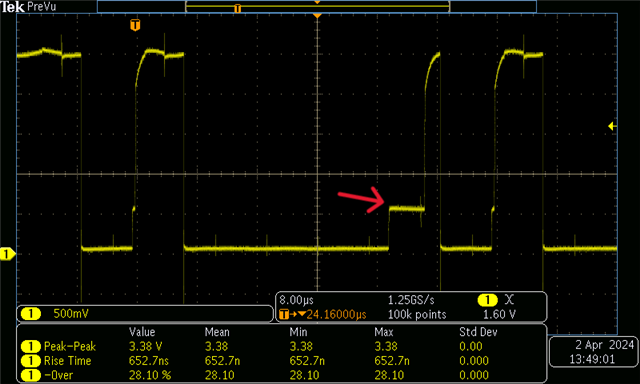

The issue we have are contention and large undershooting on I2C Bus. The function of I2C bus is also not stable. working most time but sometimes failed.

The signal of SDA looks like this:

I have reviewed TI app notes slyt770. Based on this app notes, the contention is caused by the Master output and slave output are turned on at same time. I checked the FPGA master side, it is open-drain. It seems something to do with slave devices. We believe this causes the I2C bus failed sometimes. Now my question is, why is it happen and how we can fix it?

Beside contention issue, we also see large undershooting on I2C signals. The I2C bus is 2.5V. The master and slaves are on different boards with board-board connectors.

Any help will be much appreciated.

Jeff