Hi Team,

May I ask the SDO architecture of TCAN1145-Q1? Is it a push pull architecture? Thanks.

Regards,

Ivy

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

May I ask the SDO architecture of TCAN1145-Q1? Is it a push pull architecture? Thanks.

Regards,

Ivy

Hi Ivy,

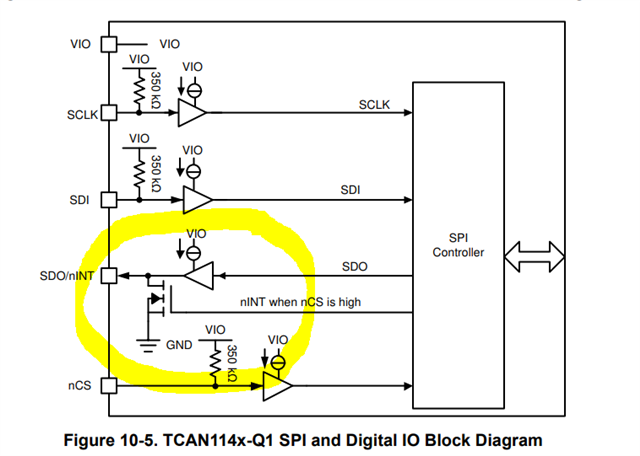

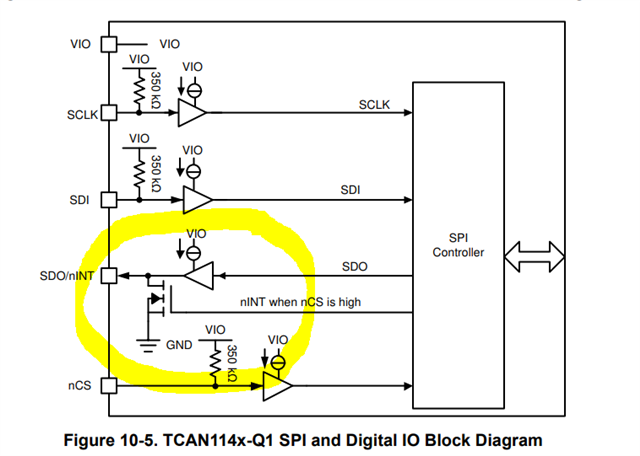

When in SDO mode, this pin has push-pull capability and the device will actively drive the signal state associated with the current bit being shifted out of the SPI controller. When the nCS signal is high, the SDO pin will be in a high impedance state in order to allow other devices to use this signal.

If the nINT function is enabled on this device, the nINT feature will be active when nCS is high. When there is no pending enabled interrupt, the nINT pin will be high impedance. When an enabled interrupt is set in the device, the nINT pin will pull-low (open drain output) to indicate the interrupt. When nCS is asserted low, this pin will go back to SDO mode and will be push-pull again.

Let me know if you have any more questions.

Regards,

Eric Schott