Hi team,

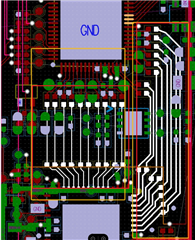

The customer currently uses the dual PORT inputs of 947. LVDS shares a set of clock inputs. I understand that D0- and D0+ must be of equal length.

On the same port, for example:

Within what error do the trace lengths of D0+D0- of Port0 and D1+D1- of Port0 need to be controlled?

Do the lanes between different ports need to be of equal length, for example:

Do the trace lengths of D0+D0- of Port0 and D7+D7- of Port1 need to be controlled to be the same length? If necessary, what is our error requirement for trace length?