Part Number: DP83867E

Other Parts Discussed in Thread: DP83869HM,

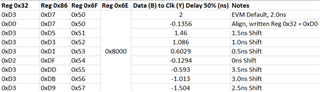

When configuring DP83867 or DP83869HM (aka DP8386x) for RGMII communication, there two RGMII modes that the PHY can be strapped into; shift or align. In align mode, there is no skew between RGMII Clock, Data, and CTRL. In shift mode, the PHY can be strapped to shift the Data/CTRL relative to Clock in 0.5ns increments. This can be further refined into 0.25ns increments via register writes in Reg 0x86.

These delays can be programmed for the TX and RX portions of the RGMII bus independently. When RX is configured, the output is shifted and is shown on the RX traces. When TX is configured, the input is shifted within the PHY, and thus any scope measurement would need to account for the internal delay.

Below are sample data collected from DP83867ERGZ-R-EVM measuring the RX skews while varying strapping of the PHY.